## Synchronization and Sequencing of Data Acquisition and Control Electronics at the European X-Ray Free Electron Laser

Vom Promotionsausschuss der Technischen Universität Hamburg-Harburg

zur Erlangung des akademischen Grades

Doktor Ingenieur

genehmigte Dissertation

von Patrick Geßler

> aus Hamburg

> > 2015

Prof. Dr-Ing. Dr. h.c. Klaus Schünemann Prof. Dr. F. Mayer-Lindenberg Prof. Dr.-Ing. Wolfgang Krautschneider

20. November 2015

#### Abstract

The 3.5km long European X-Ray Free Electron Laser, currently under construction in northern Germany, will deliver bursts of up to 2700 short x-ray pulses every 100ms, providing wavelengths between 0.05 and 6 nm, and a repetition rate of 4.5MHz to several experiment stations. It allows in-depth research in various scientific fields.

In order to set-up the beam, position samples and capture the measured variables, information from the accelerator, diagnostic devices and detectors have to be digitized, converted, processed, transferred, concentrated, distributed, reorganized, controlled and saved. All these steps have to be accurately synchronized and sequenced relative to the actual electron bunch or photon pulse in order to guarantee correct data acquisition timings and unique identification of each bunch passing the beamlines.

This document provides a complete description of the planning, design, realization and evaluation of the European XFEL Timing System, which implements the synchronization and sequencing of the data acquisition and control electronics for the European X-Ray Free-Electron Laser Facility.

## Contents

| 1        | $\operatorname{Intr}$ | oduction 1                                                                                                  |

|----------|-----------------------|-------------------------------------------------------------------------------------------------------------|

|          | 1.1                   | Motivation                                                                                                  |

|          | 1.2                   | Deutsches Elektronen-Synchrotron (DESY) 1                                                                   |

|          | 1.3                   | European X-Ray Free-Electron Laser Facility                                                                 |

|          | 1.4                   | Scope of work                                                                                               |

|          | 1.5                   | Requirements                                                                                                |

|          |                       | 1.5.1 Required functions                                                                                    |

|          |                       | 1.5.2 Bunch structure                                                                                       |

|          |                       | 1.5.3 Frequencies                                                                                           |

|          |                       | 1.5.4 Stability requirements                                                                                |

|          |                       | 1.5.5 Hardware platform                                                                                     |

|          | 1.6                   | Structure of this document                                                                                  |

| <b>2</b> | Defi                  | nition of terms 7                                                                                           |

|          | 2.1                   | Timing System                                                                                               |

|          | 2.2                   | Clock                                                                                                       |

|          | 2.3                   | Trigger                                                                                                     |

|          | 2.4                   | Gate                                                                                                        |

|          | 2.5                   | Syntonization                                                                                               |

|          | 2.6                   | Synchronization                                                                                             |

|          | 2.7                   | Deterministic data transmission                                                                             |

|          | 2.8                   | Drift                                                                                                       |

|          | 2.9                   | Noise                                                                                                       |

|          | -                     | 2.9.1 Thermal Noise                                                                                         |

|          |                       | 2.9.2 Shot Noise                                                                                            |

|          |                       | 2.9.3 Flicker Noise and $1/f^n$ -Noise                                                                      |

|          |                       | 2.9.4 Burst Noise                                                                                           |

|          |                       | 2.9.5 Amplitude, Frequency and Phase Noise                                                                  |

|          | 2.10                  | $\begin{array}{c} \text{Jitter} & \dots & $ |

|          |                       | Time Interval Error                                                                                         |

|          |                       | Dispersion                                                                                                  |

|          |                       | Inter Symbol Interference (ISI)                                                                             |

|          |                       | Resolution                                                                                                  |

| 3        | Tim                   | ing system technologies and usage at Light Sources 15                                                       |

| 9        | 3.1                   | Distribution of Coordinated Universal Time (UTC)                                                            |

|          | 0.1                   | 3.1.1 Network Time Protocol (NTP)                                                                           |

|          |                       | 3.1.2 IEEE1588, SyncE and White Rabbit                                                                      |

|          | 3.2                   | Bunch clock distribution system                                                                             |

|          | 0.4                   | 3.2.1 European Synchrotron Radiation Facility (ESRF)                                                        |

|          |                       | 5.2.1 European Synchronon Radiation Facility (ESIT)                                                         |

|   |                 | 3.2.2 PETRA III                                                                                                                          |

|---|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.3             | Clock and event distribution systems                                                                                                     |

|   |                 | 3.3.1 FLASH Event System                                                                                                                 |

|   |                 | 3.3.2 Micro-Research Finland (MRF)                                                                                                       |

|   |                 |                                                                                                                                          |

| 4 | $\mathbf{Syst}$ | tem design 23                                                                                                                            |

|   | 4.1             | Basic concept                                                                                                                            |

|   | 4.2             | Implementation of the basic concept                                                                                                      |

|   | 4.3             | Influences on phase stability                                                                                                            |

|   |                 | 4.3.1 Temperature induced drift                                                                                                          |

|   |                 | 4.3.2 Jitter                                                                                                                             |

|   |                 | 4.3.3 Electro Magnetic Interference (EMI)                                                                                                |

|   |                 | 4.3.4 Conversion of amplitude into phase variations                                                                                      |

|   | 4.4             | Influences on accuracy                                                                                                                   |

|   |                 | 4.4.1 Resolution                                                                                                                         |

|   |                 | 4.4.2 Reproducible phase relations                                                                                                       |

|   | 4.5             | Consequences for the system design                                                                                                       |

|   | 1.0             | 4.5.1 Synchronization to power line frequency                                                                                            |

|   |                 | 4.5.2 Optical transmission line and interfaces                                                                                           |

|   |                 | 4.5.3 Drift compensation scheme                                                                                                          |

|   |                 | 4.5.3 Difft compensation scheme                                                                                                          |

|   |                 | 4.5.5 Dedicated low-jitter clock section                                                                                                 |

|   |                 |                                                                                                                                          |

|   |                 | 0 0                                                                                                                                      |

|   | 1.0             | 4.5.7 Receiver-side clock and trigger synchronization                                                                                    |

|   | 4.6             | Selection of components                                                                                                                  |

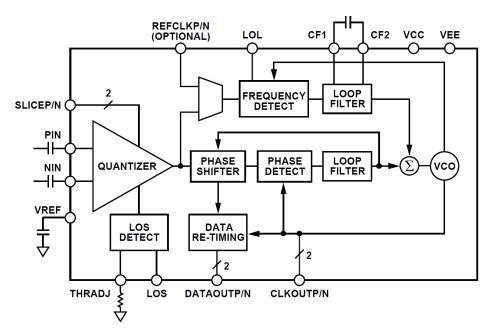

|   |                 | 4.6.1 Clock and Data Recovery (CDR)                                                                                                      |

|   |                 | 4.6.2 Field Programmable Gate Array (FPGA) 38                                                                                            |

|   |                 | 4.6.3 Phase detector                                                                                                                     |

|   |                 | 4.6.4 Adjustable delay                                                                                                                   |

|   |                 | 4.6.5 Clock dividers and output buffers                                                                                                  |

|   |                 | 4.6.6 Switches and buffers $\ldots \ldots 41$                             |

|   |                 | 4.6.7 Phase Locked Loops (PLLs) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 41$                                      |

|   |                 | $4.6.8  \text{Optical transceivers}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                    |

|   |                 | 4.6.9 Fibers                                                                                                                             |

| _ | -               |                                                                                                                                          |

| 5 |                 | luation 43                                                                                                                               |

|   | 5.1             | Investigation of critical components                                                                                                     |

|   |                 | 5.1.1 Delay, CDR and clock dividers                                                                                                      |

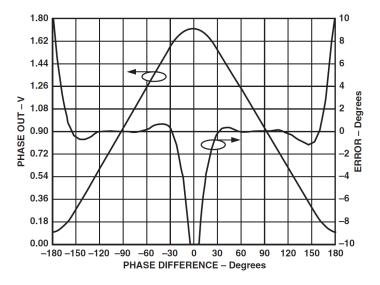

|   |                 | 5.1.2 Phase detector $\dots \dots \dots$ |

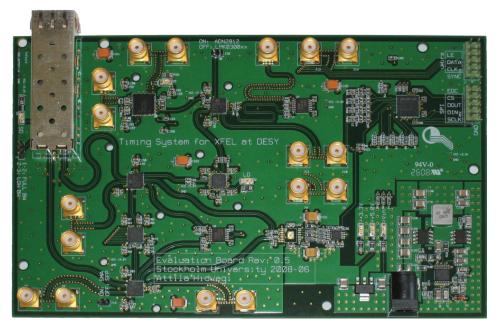

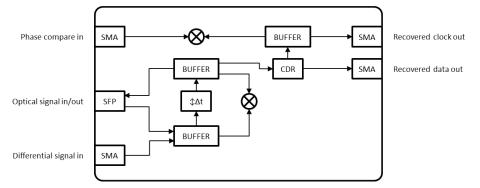

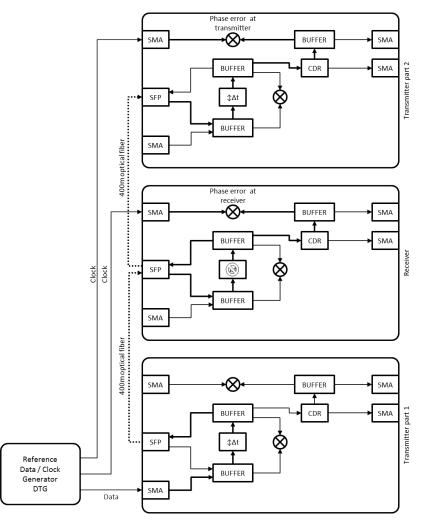

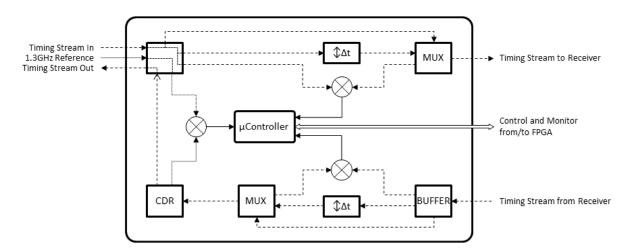

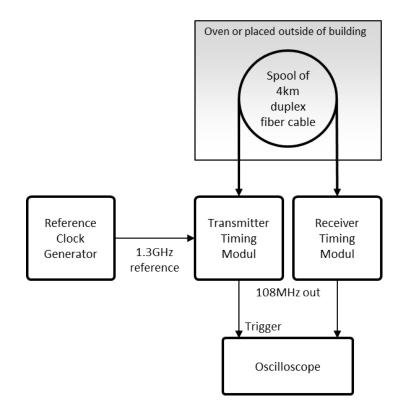

|   | 5.2             | Evaluation board and measurement setup 47                                                                                                |

|   | 5.3             | Implementation of the drift compensation scheme                                                                                          |

|   |                 | 5.3.1 Phase stabilization with fine delays                                                                                               |

|   |                 | 5.3.2 Control of coarse delays $\ldots \ldots 50$                  |

|   |                 | 5.3.3 Adjustments of non-symmetric delay elements                                                                                        |

|   | 5.4             | Measurement results                                                                                                                      |

|   |                 |                                                                                                                                          |

| 6 |                 | roTCA hardware platform 53                                                                                                               |

|   | 6.1             | Time of transition $\ldots \ldots 53$         |

|   | 6.2             | Introduction to ATCA and MicroTCA 54                                                                                                     |

|   | 6.3             | Features of the MicroTCA standard                                                                                                        |

|   |                 | 6.3.1 Passive Backplane                                                                                                                  |

|    |        | 6.3.2 Management of modules and hot-plugging                                        |  |  |

|----|--------|-------------------------------------------------------------------------------------|--|--|

|    |        | 6.3.3 Centralized switching and distribution                                        |  |  |

|    |        | 6.3.4 Point-to-point connections                                                    |  |  |

|    |        | 6.3.5 Redundancy                                                                    |  |  |

|    |        | 6.3.6 Remote access                                                                 |  |  |

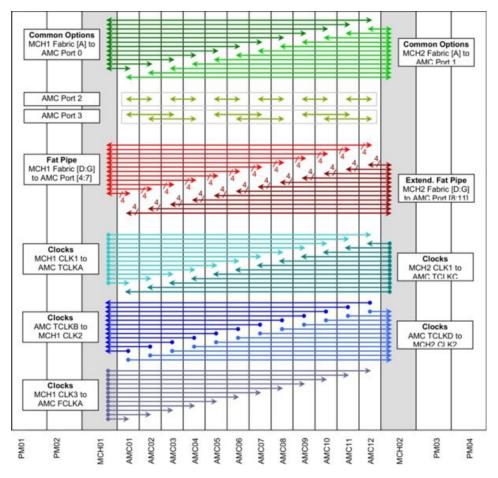

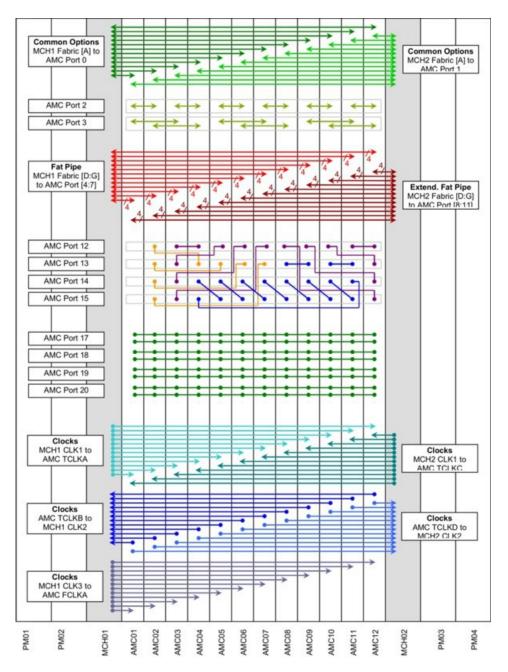

|    | 6.4    | xTCA for Physics working group and MTCA.4 standard                                  |  |  |

|    |        | 6.4.1 Distribution of slow clocks, triggers, interlocks and deterministic data . 59 |  |  |

|    |        | 6.4.2 Double Size AMCs and Micro Rear Transition Modules                            |  |  |

|    |        | 6.4.3 High-Speed serial point-to-point interconnects                                |  |  |

|    |        | 6.4.4 Improvements on noise and jitter                                              |  |  |

|    |        | 0.4.4 Improvements on noise and jutter                                              |  |  |

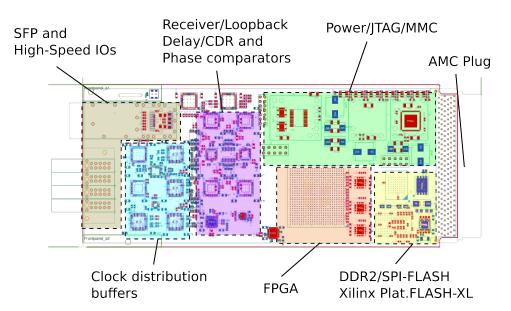

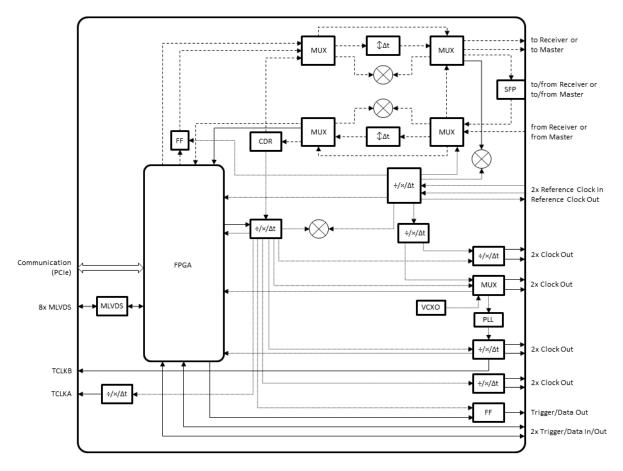

| 7  | Firs   | First generation Timing System board                                                |  |  |

|    | 7.1    | Hardware                                                                            |  |  |

|    | 7.2    | Reference clock and triggers                                                        |  |  |

|    | 7.3    | Timing data stream transmission and drift compensation                              |  |  |

|    | 7.4    | Timing receiver                                                                     |  |  |

|    | 7.5    | Clock distribution                                                                  |  |  |

|    | 7.6    | Triggers, bunch clocks and data outputs                                             |  |  |

|    | 7.7    | Further options                                                                     |  |  |

|    | 7.8    | Experience and consequences for next generation                                     |  |  |

|    |        | 7.8.1 Form factor and module separation                                             |  |  |

|    |        | 7.8.2         Clock buffers         68                                              |  |  |

|    |        | 7.8.3         Connectors         69                                                 |  |  |

|    |        | 7.8.4       Filtering of power supply       69                                      |  |  |

|    |        | 7.0.4 Fintering of power supply 03                                                  |  |  |

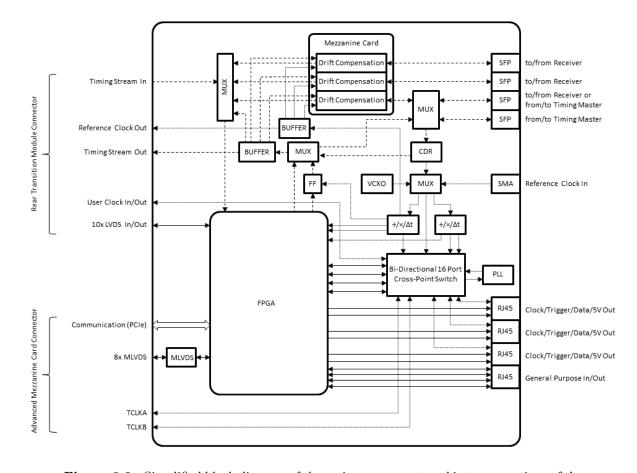

| 8  | Seco   | ond generation Timing System board 71                                               |  |  |

|    | 8.1    | Hardware $\ldots$ $\ldots$ $\ldots$ $71$                                            |  |  |

|    | 8.2    | Reference clock and triggers                                                        |  |  |

|    | 8.3    | Timing receiver                                                                     |  |  |

|    | 8.4    | Clock distribution                                                                  |  |  |

|    | 8.5    | Trigger, bunch clock and data outputs                                               |  |  |

|    | 8.6    | Timing data stream transmission and drift compensation                              |  |  |

|    | 8.7    | Extending the functionalities                                                       |  |  |

|    |        | Complete drift compensation measurement                                             |  |  |

|    | 0.0    |                                                                                     |  |  |

| 9  | Firr   | nware 81                                                                            |  |  |

|    | 9.1    | Configuration of integrated circuits on the module                                  |  |  |

|    | 9.2    | Generation of the timing data stream                                                |  |  |

|    | 9.3    | Control loop for drift compensation                                                 |  |  |

|    | 9.4    | Synchronization to the timing data stream                                           |  |  |

|    | 9.5    | Decoding of the timing data stream                                                  |  |  |

|    | 9.6    | Trigger generation                                                                  |  |  |

|    | 9.7    | Transmission of deterministic data to local receiving systems                       |  |  |

|    | 9.8    | Communication with in-crate CPU via PCIe                                            |  |  |

|    | 9.9    | Synchronization between Modules                                                     |  |  |

|    |        |                                                                                     |  |  |

|    | 9.10   | Remote Firmware Upgrade                                                             |  |  |

| 10 | ) Soft | ware 91                                                                             |  |  |

|    |        | CPU technology, operating system and interfacing                                    |  |  |

|    |        | Driver                                                                              |  |  |

|    |        | Control Systems and device implementation                                           |  |  |

|    | 10.0   | Control Systems and device imprementation                                           |  |  |

| 10.4 Graphical User Interface (GUI)             |  | . 93  |  |  |

|-------------------------------------------------|--|-------|--|--|

| 11 Interfacing to consumers                     |  | 97    |  |  |

| 11.1 Interfaces within the MicroTCA crate       |  | . 97  |  |  |

| 11.1.1 Low-jitter Clock Distribution            |  | . 97  |  |  |

| 11.1.2 Signal Distribution on M-LVDS Bus Lines  |  |       |  |  |

| 11.1.3 Interrupt and Information on PCIe        |  | . 101 |  |  |

| 11.2 RJ45 connectors for external consumers     |  | . 101 |  |  |

| 11.3 RJ45 connector for external trigger inputs |  | . 103 |  |  |

| 11.4 Future options                             |  | . 104 |  |  |

| 12 Interfacing with other Timing Systems        |  | 105   |  |  |

| 12.1 FLASH Timing System                        |  | . 105 |  |  |

| 12.2 Micro Research Finland                     |  |       |  |  |

| 12.3 White Rabbit                               |  |       |  |  |

| 12.4 Bunch clock distribution systems           |  |       |  |  |

| 13 Conclusion                                   |  | 109   |  |  |

| 14 Acknowledgments                              |  | 111   |  |  |

| List of Abbreviations                           |  | 113   |  |  |

| List of Symbols                                 |  |       |  |  |

| References                                      |  |       |  |  |

# Chapter 1 Introduction

#### 1.1 Motivation

Time and order affect almost everybody's life. Whether it is about a point in time, when to get up in the morning and when to meet friends or a customer or how long it takes to walk, drive or fly to a certain destination - time is of importance. Ordering comes into play, as soon as there is more than just one task to do - what should be done first, is there a dependency between different tasks? Usually order becomes even more important, the more tasks have to be done in a limited time, or - the other way around - the shorter the time gets. Even people who think of themselves as not following common conventions of time and order, are still bound to cycles of nature and civilization like the day-and-night cycles, the seasons of the year or opening hours of shops, respectively. They have to synchronize to these cycles - at least to some extent.

The very same is true for complex machines like the European X-Ray Free Electron Laser (XFEL), which is currently under construction in northern Germany. This 3.4km long accelerator facility will provide X-Ray pulses of unprecedented brightness for studies in physics, chemistry, life sciences and materials research. The pulses generated and used for experiments have a duration of less than 100 Femto-seconds and will be repeated up to 2700 times within a time window of 600 Micro-seconds. In order to generate these series of short pulses thousands of components (including lasers, signal generators, diagnostic systems, detectors, motors etc.) have to be synchronized and the order (sequencing) within this short time frame has to be defined in a strict way. The design, development, implementation and verification of a technical solution, which accomplishes the tasks of synchronization and sequencing for the European XFEL is the topic of this work. The realization has been named XFEL Timing System.

#### 1.2 Deutsches Elektronen-Synchrotron (DESY)

The Deutsche Elektronen-Synchrotron (DESY) is a research center within the Helmholtz association and is located in Hamburg, Germany. The focus of the work and the main research fields have changed during the more than 50 years since the DESY had been founded in 1959. The initial interest concentrated on high energy physics, where the inner structure of particles were investigated. Particle collider accelerators were developed in order to produce collisions of different particles, which revealed most of the inner components and effects.

Over the time almost all experiments have been done with the available energy the accelerators were able to provide to the particles. This was the reason, why the biggest accelerator, HERA, reached its planned end in 2007 (although the processing and evaluation of the high amount of detected data is still ongoing).

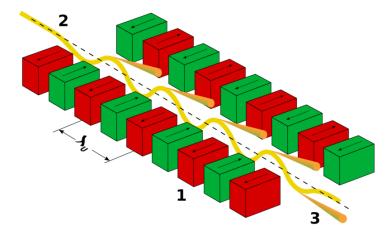

Besides particle collisions, accelerators are also a source of photons which are radiated when charged particles are accelerated. This always happens in circular accelerators, as the particles have to be kept on a circular path, which requires acceleration towards the center, even if the time for one revolution is constant. The photon production could be even highly intensified by using a special structure called wiggler (see Figure 1.1). In this structure the group of particles (2) - called bunch (in our case consisting of electrons) - will pass a certain number of magnetic fields with alternating polarizations, which are created by permanent and strong magnets (1). Each field will impose a Lorenz-force to the electron bunch, which will slightly divert the trajectory to either the right or left side (depending on the field orientation). Due to the alternating fields, the trajectory becomes a kind of zig-zag course. During that path, many photons are produced (3) and the wave length could be influenced by the distance between the upper and lower row of magnets (the so called gap size) and the energy of the electron bunch (due to the acceleration process). Usual wave lengths of photons produced are between 0.1nm and 10nm (hard to soft X-Rays). The photons generated are guided to special isolated rooms (hutches), where experiments could be carried out. These technologies have been implemented on the DESY premises at accelerators like PETRA III.

The photon pulses produced have a limited but continuous wave length, as the accelerated

Figure 1.1: Alternating structure of fixed magnetic fields (1) in order to divert the trajectory of a passing electron bunch (2) onto a zig-zag course. This will create photons (3) due to Bremsstrahlung along the way and leave the structure at the end together with the electron bunches. This structure is called Wiggler or Undulator (depending on the design properties like the magnetic field force and wave length  $\lambda_u$  and the resulting effect). (Picture from Wikipedia)

electrons will carry non-discrete energies, which are the bases for the photon generation process in the wiggler. Additionally the angle under which the photons leave the wiggler is relatively wide and no interaction of the photons is happening. However, for many experiments (especially for imaging of molecular structures) a coherent and discrete wave length photon pulse with a small angle is of great interest. Then diffraction images of investigated samples could be generated and captured with 2D image detectors. This possibility has been achieved with the development of the Free-Electron-Lasers like the existing FLASH at DESY and the European XFEL under construction - which will be introduced in the next section - and other machines world wide.

Today DESY focuses its work and research area on the following fields:

- Design, construction and operation of accelerators

- Scientific research with photons

• Scientific research in particle and astro-physics

#### 1.3 European X-Ray Free-Electron Laser Facility

The European X-Ray Free-Electron Laser (XFEL) Facility is a European project, internationally funded and built between the DESY premises in Hamburg and the adjacent federal state Schleswig-Holstein in northern Germany (see Figure 1.2). The whole machine will have an ap-

Figure 1.2: Photo of the location around the European XFEL. Starting from the DESY site in Hamburg (right side), the photons will be available in the experiment area in Schenefeld (left side). (From European XFEL picture data base)

proximate length of 3.4km and follows the Free-Electron-Laser principle (a summary of history of FELs and the European XFEL in special as well as detailed technical design information and planned research fields could be found in the Technical Design Report (TDR) [1]). On the DESY site electron bunches will be generated, when a laser pulse hits on a cathode. These bunches will be accelerated, where the imposed energy will increase with each accelerating module along the path. After acceleration and compression of the bunches, they will pass a structure called undulator, which is very similar to the previously described wiggler. The main differences are, that (1) the amplitude of the zig-zag course is smaller, which leads to a smaller angle under which the photon pulses will leave the structure, and (2) the generated photons will interact with each other by generating interference and (3) interacting with the electron bunches stimulates the photon generation effect in a way, that (4) laser pulses will be generated, which provide coherent and almost discrete wave length photon pulses. This process is called self-amplified spontaneous emission (SASE) and is the basis for the lasing effect.

The machine can logically be viewed as three parts (see again Figure 1.2 from right to left): (1) the electron accelerator - between DESY Bahrenfeld and Osdorfer Born, (2) the undulator and photon beam lines - between Osdorfer Born and Schenefeld Site - and (3) the experiment stations on the Schenefeld Site. The electron accelerator part consists of a single path, which is shared with all following sections. There the electron bunches are created, accelerated, focused, compressed and monitored. In the first junction point, the bunches are directed into different beam lines. There different undulators (in the beginning three will be available and denoted as SASE 1 to 3) will generate photons with different wave lengths, which are guided to the end of the beam lines to the experiment stations. The electron bunches will be destroyed (dumped) on the way. Per beam line, entering the experiment area, two experiment stations are planned, which add up to six altogether in the beginning. The current layout allows two more undulators, which could be added on an upgrade procedure in the future together with the related experiment stations.

The design and development of the European XFEL started in 2005. In 2009 a new limited

liability legal entity called European X-Ray Free-Electron Laser Facility GmbH was founded in order to adequately represent the international share holders and define the ownership of the machine. In this context DESY was assigned to be responsible for the construction and operation of the accelerator part of the European XFEL. The commissioning of all systems is planned for 2016 and user operation is supposed to start in 2017.

#### 1.4 Scope of work

The work described in this document is focused on the conceptual design, development, setup and evaluation of the European XFEL Timing System, which will be the technical implementation of a facility-wide clock distribution, synchronization and sequencing system for all data acquisition and control electronics at the European XFEL. Based on the author's previous studies and findings [2] and the requirements, which will be presented in the following section, a suitable and economically efficient solution has to be developed and with the support of DESY staff, external collaborators and companies, installation-ready series production level modules have to be prepared.

The following chapters will provide background information, a summary of the different design, development and evaluation phases and further information about interfacing subsystems and integration possibilities for other accelerators. In the acknowledgment section at the end of this document credit is given to all involved persons, institutions and companies, who and which contributed to the realization of this ambitious project.

#### 1.5 Requirements

This section provides an overview of the requirements of the Timing System to be developed. More detailed information and definition of terms will be provided in the following chapters and in the lists of abbreviations and symbols at the end of this document.

#### 1.5.1 Required functions

The Timing System to be developed is required to provide at least the following functions:

- Distribution and generation of derived clocks synchronized and syntonized to the RF master oscillator (see section about frequencies below)

- Distribution of events as the basis for generating time adjustable and synchronized triggers and gates

- Distribution of deterministic data related to fast changing parameters of the European XFEL (e.g. bunch pattern)

- Define the repetition rate of the macro pulse (see following paragraphs)

#### 1.5.2 Bunch structure

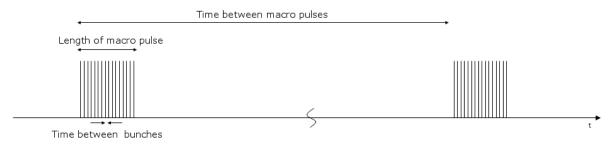

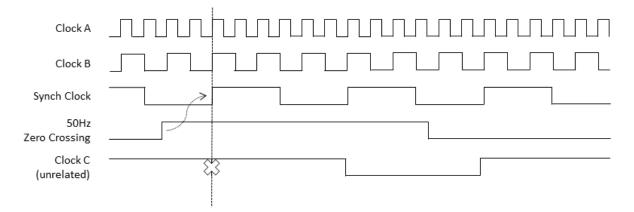

The Timing System to be developed has to be compatible with the planned bunch and time structure of the European XFEL and the existing Free-electron LASer in Hamburg (FLASH), as almost all systems under development should be compatible with both machines. Table 1.1 summarizes the important bunch and time structure parameters for both facilities and Figure 1.3 illustrates the parameters in a time diagram:

|                                        | European XFEL     | FLASH             |

|----------------------------------------|-------------------|-------------------|

| Length of macro pulse                  | $600 \mu s$       | $800 \mu s$       |

| Time between macro pulses              | $100 \mathrm{ms}$ | $100 \mathrm{ms}$ |

| Max. number of bunches per macro pulse | 2700              | 800 or 2400       |

| Min. time between bunches              | 220 ns            | 996ns or 332ns    |

Table 1.1: Summary of important bunch and time structure parameters for the European XFEL and FLASH.

Figure 1.3: Generic time structure of bunch delivery and macro pulse for the European XFEL and FLASH.

#### 1.5.3 Frequencies

The Timing System to be developed has to connect to the master oscillator of the European XFEL or FLASH and therefore has to be compatible and syntonize to the frequency and synchronize to the phase of the 1.3GHz reference of the machine. Furthermore the Timing System has to synchronize to the phase of the 50Hz voltage oscillations on the power line for deriving the 10Hz macro pulse repetition rate (see above).

Besides that, at the receiver side of the distributed timing signals, derived frequencies from the reference have to be generated, which have a fixed phase relation and maintain this relation across macro pulses. The phase relation should be kept even after a system restart or power cut. The rounded values of the most important frequencies to be provided by the receiver are shown in Table 1.2 along with their accurate divider value of the 1.3GHz reference clock:

| Generated Frequency (rounded) | Divider value for 1.3GHz |

|-------------------------------|--------------------------|

| 1.3GHz                        | 1                        |

| $216 \mathrm{MHz}$            | 6                        |

| $108 \mathrm{MHz}$            | 12                       |

| 81MHz                         | 16                       |

| 54MHz                         | 24                       |

| 9MHz                          | 144                      |

| 4.5MHz                        | 288                      |

| 1MHz                          | 1296                     |

Table 1.2: List of rounded values of most important frequencies and the accurate divider value for the 1.3GHz reference to be provided by the Timing System receiver side.

#### 1.5.4 Stability requirements

The time jitter of the distributed 1.3GHz reference clock at the receiver side should be within 10ps RMS relative to the reference clock of the master oscillator. For derived clocks at the

receiver side, which can also include user definable phase delays, a slightly higher jitter is acceptable, but should be kept as low as possible. The jitter requirement is mostly motivated by the low jitter requirements of fast analogue to digital converter (ADC) based diagnostics and detectors, which have no additional jitter cleaner in their clock input path and higher jitter would reduce the resulting signal-to-noise ratio beyond acceptable limits. In many cases fast transient signals are captured by ADCs with significant under sampling, where the phase variation between detected signal and sampling clock has to stay within boundaries as small as 10ps

The phases of generated triggers have to be as stable as required to unambiguously identify a certain clock period of the derived clocks at the receiver side (see above) - in the order of 100 ps. This number is motivated by the requirement to safely identify a certain period of the 1.3GHz frequency.

#### 1.5.5 Hardware platform

The chosen hardware platform for most of the fast data acquisition and control electronics will be MicroTCA, the Timing System to be developed has to be compatible to this standard. However, as many subsystems of the European XFEL will not be available in MicroTCA standard, also external interfaces have to be provided in order to provide timing related signals to external components.

#### 1.6 Structure of this document

The structure of this document can be divided into four parts: The first part, consisting of chapters one to three, gives an introduction to the topic, the facility and requirements (1), important terms and definitions (2) and provides an overview about timing system technologies at other light sources (3). The second part (chapters four to ten) is concerned with the actual design (4), evaluation of the design (5), a description of the two generations of developed timing system modules (7 and 8), a description of the firmware (9) and software (10) functionalities. The only exception is chapter six, which provides an introduction to the MicroTCA standard, which is required in order to understand the functionalities of the timing system modules. The third part (chapters eleven and twelve) presents how the developed timing system can be used in terms of interfacing to the consumers (11) and interfacing to other timing systems (12). Finally, the fourth part closes the work with conclusions (13) and the acknowledgments of all persons, who contributed to this project (14).

### Chapter 2

## Definition of terms

Learning vocabularies and their meaning is crucial in order to understand a foreign language. Although the terms described here are in English language and most of them are even commonly known, it is even more important to introduce them, as their interpretation might be different and partly depends on the context.

This chapter will introduce and briefly describe important terms related to timing systems, their applications and performance measures.

#### 2.1 Timing System

Although the description of the Timing System requires some of the following terms, it will be presented first in order to provide an overview in what sense the other terms relate to the actual topic of this work. This section covers important features of the timing system. More details will be provided later on in other chapters.

As the name already indicates, the timing system is a combination of different components dealing with time related signals. One important aspect of the timing system is the distribution of signals, which allow numerous subsystems along the European XFEL to work synchronously with respect to the electron bunches or photon pulses and other subsystems like analogue-to-digital converters (ADCs), processing units and digital-to-analogue converters (DACs). These systems usually require clocks in order to define the sampling or processing cycles and one or multiple triggers, which define the points in time, when to start sampling or processing. Therefore the Timing System has to be distributed and provide those signals to all subsystems in a synchronized and stable way.

Many parameters of the machine will change during the run-time like the number of bunches, the pattern of bunches, the charge, the path through the machine and so on. Those parameters influence many systems along the machine. There will always be a certain point in time, when one parameter is changed and it is important to provide a deterministic information channel via the timing system, which guarantees facility wide synchronous switch-overs of parameters. The European XFEL will operate continuously over many years. During that time a high data volume is collected from various detectors and diagnostic systems. In order to make use of these collected data, it is crucial, that data sets (e.g. values for a certain bunch) from all sources can be correlated. Therefore a unique ID or synchronized time stamp has to be assigned to all data, which identifies each single data set facility-wide. This information has to be provided by the timing system as well.

The timing system is a facility-wide distributed system, which provides the above mentioned signals and information based on a centralized reference and information provided by the operators of the machine taking its current state and allowed parameters into account.

#### 2.2 Clock

A clock is defined as a periodic signal with one rising edge per period. All other parameters like frequency, phase, signal levels and standards, shape and transport medium are context dependent. Important for clocks provided by the timing systems is the facility-wide synchronization of the phases and syntonization of the frequency. The reference frequency, provided by the master oscillator, is 1.3GHz. There are different frequencies available, but there is always a fixed phase and frequency relation between them maintained.

Common users of clocks are ADCs, DACs, FPGAs, fast serial transceivers.

#### 2.3 Trigger

A trigger is defined as a pulse, where its rising edge indicates a certain point in time. Besides the above described usage of clocks in almost all subsystems a trigger is important to indicate a point in time, when to start sampling data or when to acquire a picture or when to process data. Triggers in the same meaning are also used at oscilloscopes to define a certain point in time.

Triggers can also be periodic. For European XFEL a 10Hz cycle of recurring procedures is planned. Therefore most of the defined triggers will be periodic with 10Hz. In general the time between triggers can be long (maybe even only one time at all) or short (if used as bunch trigger, where trigger pulses can have a period in nano-second range). This is often combined with a burst mode, where the periodicity is only within a certain time window, which can then also be repeated on a regular basis.

#### 2.4 Gate

A gate is very similar to a trigger. The main difference is, that not only the rising edge of the pulse is relevant, but also the falling edge. Therefore gates are usually defined by two certain events, where the first one generates the rising edge of the signal and the second defines the falling edge.

Common application of a gate signal is to define the time frame, where certain signals are to be considered. Examples are cameras where photons are collected on a 2D detector or counters, where pulses from a detector are counted.

#### 2.5 Syntonization

Syntonization defines the property of at least two periodic signals to have the same frequency. In case of the timing system, the important aspect is to syntonize the frequencies at the end points with the reference frequency provided by the master oscillator.

The frequency f of a periodic signal is defined by the inverse of the time of one period  $t_{period}$ .

$$f = \frac{1}{t_{period}}$$

The phase of a periodic signal can be defined as

$$\phi(t) = 2\pi f t + \phi_0$$

where  $\phi_0$  is the initial phase.

If two periodic signals with the same frequency f start with the same phase  $\phi_0$ , the phase

between them will be maintained for all values of time t.

$$\Delta\phi(t) = \phi_1(t) - \phi_2(t) = (2\pi f t + \phi_0) - (2\pi f t + \phi_0) = 0$$

(2.1)

However, if the frequency is only slightly different, the phase relation between both signals will change over time:

$$\Delta\phi(t) = \phi_1(t) - \phi_2(t) = (2\pi f_1 t + \phi_0) - (2\pi f_2 t + \phi_0) = 2\pi t (f_1 - f_2)$$

(2.2)

The time dependent phase difference has some undesirable effects:

- Especially in sampling applications at frequencies between 1MHz to 200MHz the sampling point should be adjusted to capture certain points of a period of a signal (e.g. the peak and baseline). If the phase of the sampling frequency is not constant with respect to the signal to be captured, it is not possible to sample fixed points during one period. If the sampling frequency phase is changing, the desired sample points will not be maintained.

- Usually triggers are used to define a certain point in time during data acquisition or processing. In most applications the next rising edge of a clock after the trigger is used to act like starting the sampling process. The trigger and the phase of the clock have to maintain a fixed relation in order to provide enough setup and hold time to reliably identify the trigger point. If the phase between the trigger (or more precisely the clock used to generate the trigger) is changing compared to the used clock, a variable time is added to each of the trigger events.

- In high speed sampling application (e.g. in GHz range) the provided frequency is multiplied in order to provide the high sampling frequencies. If the base frequency is slightly higher or lower than the frequency of the signal to be digitized, the number of samples to capture will be higher resp. lower in order to digitize the complete signal.

Syntonized frequencies are limited to exactly the same frequency. However, in real applications also other frequencies have to be generated at the timing system endpoints. In this case, another frequency  $f_2$  is generated by dividing and/or multiplying frequency  $f_1$  by an integer value. In this way a fixed frequency relation is maintained over time.

#### 2.6 Synchronization

The term synchronization defines certain properties of at least two signals to happen at the same time (with finite accuracy). Two examples are the rising edge of triggers or clocks at different timing system endpoints.

The problem of time dependent phase differences as a consequence of un-syntonized frequencies have been discussed previously. Here the effect of (un-)synchronized phases between two signals with syntonized frequencies will be discussed.

If we assume the general case of equation (2.1), where the initial phase  $\phi_0$  can be different for both signals and denoted as  $\hat{\phi}_1$  and  $\hat{\phi}_2$  it results in

$$\Delta\phi(t) = \phi_1(t) - \phi_2(t) = \left(2\pi f t + \hat{\phi}_1\right) - \left(2\pi f t + \hat{\phi}_2\right) = \hat{\phi}_1 - \hat{\phi}_2 \tag{2.3}$$

The previous equation defines, that the phase difference between the two signals is constant, but depends on the initial phases. Assuming, that the two signals could be the clocks of two timing system endpoints or the reference frequency from the master oscillator, this will result in different potential problems:

- If the phase between clocks is arbitrary, the phase has to be adjusted in order to find the correct phase for certain applications (e.g. the sampling points of a signal).

- If the initial phase is arbitrary and different on every system start-up, the previous adjustment has to be repeated every time

Similar synchronization problems occur, if a clock is divided at the timing system endpoints. The point in time, when the dividing process is started, defines the initial phase. Therefore, uncertainty of this point in time will lead to the very same problems discussed above. Solutions to these problems involve synchronization of the initial value of the dividers and point in time to start the process, which will be discussed in the following chapters as well as the synchronization of triggers.

#### 2.7 Deterministic data transmission

There are many parameters to be adjusted in order to operate a large machine like the European XFEL. Most of them are specific to certain subsystems and have no or just limited influence on other systems. Some parameters, however, are crucial and have very strong influence on almost all subsystems. If one of these parameters is changed, other systems have to react on this ideally exactly at the time when it has been changed. Such crucial parameters include the number of bunches to be generated, the charge of the bunches, the way they take through the machine etc. All these parameters are defined by the operators. Changes have to be validated with the machine protection system, that they lead to an allowed operation state and then can be applied system-wide at the same time in a synchronized way. Usual network connections do not provide deterministic transmission of the data in order to guarantee in-time delivery and synchronous evaluation of the parameters. Therefore the timing system has to implement a distribution channel for such data.

Along with other information (e.g. time stamps and unique identifiers) the timing system has to distribute this information and provide it to all interested consumers in a synchronized way. It has to be early enough in order to apply changed parameters to local systems before the actual bunches will be generated and injected. This system is denoted as deterministic data transmission.

#### 2.8 Drift

The term drift will be used to define a time-variant change of certain parameters within a longer time frame (days down to milliseconds). The most important influencing parameter is the phase of clocks. Predominant cause of such drifts are temperature changes, which could influence propagation delays in fibers, copper cables or traces. It affects integrated circuits, which can also induce voltage changes, which indirectly can lead to phase changes. These effects will be discussed more detailed in the following chapters.

#### 2.9 Noise

Noise can be defined as undesired influences on amplitude and phase of a signal. Noise can be divided into two types: deterministic and stochastic noise. Deterministic noise is mostly caused by a component in the system design and, if identified, can be removed or at least reduced in most cases. One example of deterministic noise is an undesired periodic distortion introduced by the switching frequency of a DC/DC converter. If not included in the design in the right way it can influence connected circuits in an undesired way. Deterministic noise is

characterized by non-stochastic effects generated by certain components or technologies. Stochastic noise is visible as a random signal fluctuation. There are different known and for this application partly relevant causes producing stochastic noise like thermal noise [3] [4], shot noise [5], flicker noise, and burst noise which will be described briefly.

#### 2.9.1 Thermal Noise

Thermal noise (also known as Johnson or Nyquist noise) is introduced by thermal agitation of the electrons. These fluctuations do not depend on the current, voltage or frequency. The power spectral density resulting from voltage fluctuation of a resistive conductor is calculated as

$$\bar{v_n^2} = 4k_BTR$$

where R is the resistance of the conductor in Ohms, T the temperature in Kelvin and  $k_B$  is Boltzmann's constant in Joules per Kelvin [3] [4].

As the value does not depend on frequency, it represents a horizontal line in the power spectrum and is also referred to as white noise.

#### 2.9.2 Shot Noise

Shot noise arises from the fact, that electrons carry a discrete charge and the number of electrons emitted by a source fluctuates slightly over time. Especially in cases, where potential barriers have to be crossed, the effect becomes visible as a stochastic effect and not as continuous flow of charges. This effect becomes more visible, if the number of electrons is small (meaning low currents), as then the signal to noise ratio becomes smaller. For higher currents the overall noise becomes dominated by other noise sources. This is why it is of less importance for the timing system described in this document. More details on shot noise are given in the original documents from W. Schottky [5] and J.B. Johnson [6].

#### **2.9.3** Flicker Noise and $1/f^n$ -Noise

Based on the previously cited publications [5] and [6], J.B. Johnson measured an effect, which deviated from the theory. For lower frequencies the noise was significantly higher than expected. Based on those measurements W. Schottky later described that effect as "Funkelrauschen", which has been translated into English as flicker noise, as it describes a flicker-like effect on the surface of the cathode used in the experiments. This effect defines a  $1/f^2$  noise behavior and strongly depends on the used material.

This effect relates to the so-called 1/f-noise, which generally describes noise effects, whose power spectral density attenuates with increasing frequency. Due to that characteristic the effect becomes visible at lower frequencies, where it might dominate over other noise sources. In oscillators and RF mixing techniques, where base band signals are shifted to higher frequencies, existing 1/f-noise from the base band might be shifted up to higher frequencies and can dominate the noise behavior.

1/f and  $1/f^2$  noise (also denoted as pink resp. red noise) often becomes visible in phase noise measurements as used in this document. Main causes are semiconductor based circuits like amplifiers and buffers.

The original publications on that topic are found in [7] and [8].

#### 2.9.4 Burst Noise

Burst noise is a phenomenon observed in semiconductors (first observed in the operational amplifier 709). Other names for the effect are popcorn noise or random telegraph signal. The

effect creates random offset voltage jumps in the range of microvolts over time periods of milliseconds up to seconds. Some more detailed information about this effect can be found in application notes from integrated circuit manufacturers like [9] and [10].

#### 2.9.5 Amplitude, Frequency and Phase Noise

In general noise effects can influence the stability of signals. For applications, where digital signals are processed, amplitude fluctuations are usually not as critical as phase or frequency fluctuations. However, depending on the transmission and processing technologies used, a conversion between all three types of fluctuations is possible. A simple example is the reception of a transmitted signal. In the receiver an electrical or optical signal has to be detected. Real signals do not follow an ideal rectangular shape (mostly due to band limited communication channels or drivers), but have finite rising and falling edges. Amplitude noise on these edges can lead to a time fluctuation in the detectors, as a transition might be detected too early (if the noise increased the amplitude slightly) or too late (if the noise reduced the amplitude of the rising edge). The phenomenon is usually called AM-to-PM conversion. An example of frequency noise would be a voltage controlled oscillator (VCO), where the frequency can be changed based on a change on the input voltage of the device. Therefore amplitude noise on the input voltage can change a signal transmission delay of the signal passing through the device would introduce a phase noise, if the input voltage is carrying noise.

Even if noise on currents and voltages will only introduce amplitude fluctuations, they might be converted into frequency or phase noise via additional components in a general non-linear way. Special care has to be taken in order to reduce influence of noise on system stability.

#### 2.10 Jitter

Jitter is a measure of integrated phase noise. In many cases the phase noise spectrum is not of main interest. It is more important to know the expected RMS value of the phase fluctuations of a signal (within a certain time window). One way of measuring this value is to measure the phase noise spectrum and calculate the RMS jitter value by integrating the phase noise spectrum over the relevant frequency range. A way of defining the relevant frequency range relative to the carrier is to set the lower boundary to the value, where the changes are regarded as drifts (e.g. 1kHz). The higher value might be defined by the physical limitations of the user of the signal. In most cases, the contribution to jitter from higher frequencies is very low, so that the higher boundary is of limited relevance.

An alternative way to determine the jitter of a periodical signal is described in the next section and is defined as Time Interval Error measurement.

#### 2.11 Time Interval Error

The time interval error measurement is an alternative way to measure the jitter of a periodic signal. The measurement can be done in the following way: the signal is measured with an oscilloscope at much higher frequency as the periodic signal to be investigated. Software can then calculate the average period of the digitized signal and afterwards calculate the deviation of each cycle in the data trace. The result represents the individual time interval errors and allows to calculate peak-to-peak deviations, RMS deviations, standard deviations and even histograms and spectral information of the measured data. However, the accuracy of the measurements is limited by the stability and value of the sampling frequency as well as on the vertical resolution and internal noise sources.

#### 2.12 Dispersion

Dispersion in the context of signal transmission over optical fibers describes the dependency of the phase delay on the wave length of the signal. High speed serial signals, like the ones used for timing system signal distribution, require high bandwidth in the order of multiple GHz. All frequency components of the transmitted signal will pass the fiber with different phase delays resulting in a common group delay [11]. The side effect of the dispersion is a broadening of the transmitted data pulses.

The dispersion also depends on the fiber and on the wave length of the carrier. Different possibilities exist in order to reduce or compensate the dispersion effect on the transmitted data signal and will be discussed in a later chapter and can also be found in [11] [12]

#### 2.13 Inter Symbol Interference (ISI)

Inter Symbol Interference (ISI) is closely related to dispersion. If one data word is denoted as symbol and transmitted over a medium, the data word can be recovered on the receiver side by detecting the symbol. However, due to dispersion or other effects, the symbols can be stretched over time on the way through the medium and two or more symbols can be overlapped at the receiver side. This is defined as ISI.

If ISI can not be avoided, there are solutions available in order to reconstruct the individual symbols if the concrete effect of the medium is known. More information on this topic can be found in [13]

#### 2.14 Resolution

The resolution of the timing system, as used in this document, defines the smallest step in time for events, which can be adjusted system-wide without influencing all other events. It therefore depends on the internal time base of the timing system and defines its granularity. In most cases the granularity is defined by the period of the reference clock or a subharmonic of it.

### Chapter 3

## Timing system technologies and usage at Light Sources

Timing and synchronization is an important aspect of the European XFEL as it is for other light sources, accelerators and industry applications. Before starting to go into the design details of the Timing System for the European XFEL, this chapter will provide an overview of different technologies available in order to implement timing systems as well as some information about which facilities are using them. This overview will not be complete, as many different implementations and variations exist. Therefore it focuses on general concepts and example implementations.

There are different ways of categorizing timing systems and structuring this chapter. The one chosen here is based on the type of time referencing pursued and finally provided by the described timing systems. Following this way, one could divide the timing systems into three categories: (1) distribution of coordinated universal time, (2) bunch clock distribution and (3) clock and event distribution. Those will be described in the following sections along with example implementations providing different levels of accuracy and stability.

#### 3.1 Distribution of Coordinated Universal Time (UTC)

The coordinated Universal Time (UTC) were defined officially in 1961. It provides a universal time base, from which all local time zones can be derived.

Timing Systems of this category have the main purpose of distributing this universal time to numerous end points by maintaining the accuracy and stability required for the dedicated application.

#### 3.1.1 Network Time Protocol (NTP)

The Network Time Protocol (NTP) [14] is a famous member of this timing system category. The task of this protocol is to distribute the universal time within the Internet via packetbased lower level protocols. In this environment variable latencies are expected, as the packets will pass switches and routers on the way, which store and forward the packets with variable time. Also packet losses are possible, as NTP uses state-less UDP (User Datagram Protocol) for transmission. NTP provides a distribution system for UTC to computers connected to the Internet and takes the described boundary conditions into account.

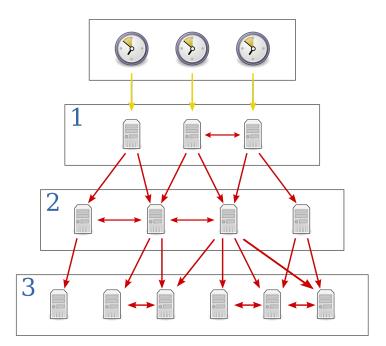

The Network Time Protocol defines a hierarchy of clock sources, called strata (see Figure 3.1). The highest level is Stratum 0 and denotes devices providing the UTC directly like atomic, GPS, radio or other clocks. Those are connected to computers, which usually act as NTP servers. These computers are defined as Stratum 1. They act as the time bases for the next

computers level (Stratum 2), which are sending NTP requests to the Stratum 1 devices. This will go on in the same way between further Stratum layers as shown in Figure 3.1.

Figure 3.1: Hierarchy in a Network Time Protocol system. Highest layer (Stratum 0) defines clock sources which are directly connected to the Stratum 1 layer (yellow arrows). Further Stratum layers will communicate with other computers over network (red arrows). (©B.D. Esham)

NTP uses 64bit time stamps in order to define a point in time. The upper 32 bits define the seconds since January 1, 1900 and the lower 32 bits the fraction of a second, providing a resolution of 233ps. The time stamp size is expected to be doubled in size in the future avoiding roll overs of the seconds part and provide higher resolution.

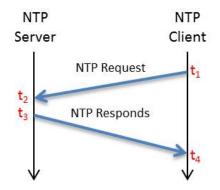

When a client receives the current time stamp from the NTP server, it gets the absolute time as it was sent by the server. In order to adjust for the transmission delay, it uses a delay measurement depicted in Figure 3.2. The NTP client sends a NTP request to the NTP server and saves its local time stamp  $(t_1)$ , when the request was sent. The NTP server saves a time stamp when the request was received  $(t_2)$ . It processes the request and sends back a packet with the send time  $(t_3)$  and also the time stamp  $t_2$ . When the client receives the packet it

Figure 3.2: Measurement of time delay between NTP server and client.

saves the time stamp  $t_4$  and can then calculate the transmission delay by

$$\Delta t_{server-client} = \frac{(t_4 - t_1) - (t_3 - t_2)}{2} \tag{3.1}$$

It is the time between sending the request and receiving the reply minus the processing time at the server side and then divided by two in order to just count one trip (server to client).

The underlying principle assumes symmetry of the transmission time for request and reply. In real systems this is not true. Deviations from symmetry introduce uncertainties and therefore errors in the transmission delay calculation and the calculated absolute time. This could be improved by using more than one NTP server as reference and calculating averages as well as removing NTP servers from the list, if they deviate too much from the expected value and therefore might be wrong.

Performance measurements showed, that accuracies between tens of micro seconds RMS (LAN) and 60ms RMS (world wide Internet) are typical for NTP [15].

#### 3.1.2 IEEE1588, SyncE and White Rabbit

White Rabbit, known from Charles Lutwidge Dodgson's (alias Lewis Carroll) novel "Alice's Adventures in Wonderland" [16] as a creature always concerned about punctuality, is the code name for a timing system implementation designed at CERN<sup>1</sup> with other laboratories and industry. The concept of this system is to combine established industry standards related to timing and synchronization and extend them in order to achieve stabilities and accuracies beyond their limits. The implementation is built on Gigabit Ethernet as defined in IEEE802.3 in variant 1000BASE-X.

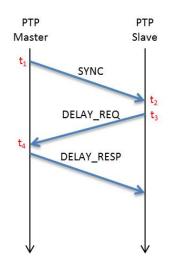

IEEE1588 defines a Precision Time Protocol (PTP), which allows to synchronize clocks of multiple slave nodes in an Ethernet network to a master clock using the coordinated universal time (UTC). In order to achieve this it is crucial to determine the transmission delay between the master and the slave in order to compensate for it (see Figure 3.3). The link delay is

Figure 3.3: Time flow diagram of the link delay measurement procedure of IEEE1588.

measured by special procedures similar to the NTP implementation, where the master sends a packet with a time stamp from its own clock at transmission time  $(t_1)$ . A slave receives it and saves the time when it was received relative to its own (currently unsynchronized) clock

<sup>&</sup>lt;sup>1</sup>European Organization for Nuclear Research, http://www.cern.ch, CH-1211, Gen'eve 23, Switzerland

$(t_2)$ . Then the slave sends at time  $t_3$  a packet to the master which will be time stamped by the master at receiving time  $t_4$  and this number then sent back to the slave. Finally the slave is able to calculate the link delay between master and slave as

$$\Delta t_{master-slave} = \frac{(t_4 - t_1) - (t_3 - t_2)}{2} \tag{3.2}$$

The accuracy of this system depends mainly on two aspects:

- Symmetry of link delays: the protocol assumes, that the link delay is symmetric in order to determine the transmission delay between master and slave by dividing the round trip time measured by two. In real networks this is not true in all cases.

- Delays of other components: Besides the link delay, there are other sources of variable and fixed delays in the communication channel, which are not considered. Examples are uncertain latency in serializer/de-serializer (PHY) chip and store-and-forward switches in the communication path.

Even if the time stamping of the packets is done in hardware in order to not rely on nondeterministic software layers defining the time information and switches are excluded the accuracy of synchronization is limited to tens of nanoseconds [17].

In ordinary Ethernet networks each communication node has its own reference clock, which is used to prepare and process the data. However, especially on high-speed Ethernet communications channels like 1Gb (1000BASE-X) and 10Gb Ethernet each receiver has to recover the clock of the sender in order to be able to detect the bits correctly. In ordinary networks the data is afterwards transferred in the local clock domain of the node to be further processed. This clock domain crossing introduces uncertainties related to synchronization and the use of local unsynchronized oscillators eliminates syntonization. The solution to this problem is implemented by Synchronous Ethernet (SyncE). In that implementation the node in the network will use the recovered clock for the internal processing and for data transmission. This eliminates the need of crossing clock domains and also provides identical frequencies at all nodes on the network.

White Rabbit combines SyncE and IEEE1588 in order to provide syntonicity and synchronicity in the network. The combination of both protocols allows to reduce the amount of resynchronization procedures of IEEE1588, as the clocks run with exactly the same frequency and therefore only changes in link delay could cause de-synchronization. But the accuracy of the system is still limited to tens of nanoseconds. In order to improve the system to sub-nanosecond precision additional hardware and protocol changes are implemented:

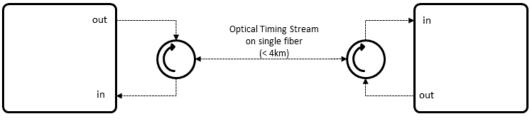

- Reduction of asymmetries: in order to reduce asymmetric behavior, transmission is done with a single optical fiber, where both sides transmit at different wavelengths (usually 1310nm and 1550nm). Delay differences for the different wavelengths are defined by the diffraction indices and are theoretically known and could even be measured for a certain installed fiber for demanding applications.

- Determination of transmitting and receiving latencies: common serializer/de-serializer chips have an uncertainty of latency due to an internal PLL and dividers, which starts up with an arbitrary phase relation. In order to eliminate the latency uncertainty it is measured and compensated for within an FPGA.

- Increasing of time stamp resolution: the accuracy of the IEEE1588 procedure is limited to the single packet boundaries (for 1Gb Ethernet it is 125MHz which is 8ns). In order to increase the resolution a phase comparator is implemented in the FPGA to measure fractions of the packet size (below nanoseconds).

- Related to the previous points, the protocol of the IEEE1588 have been extended in order to allow detection of compatible nodes, provide special data for calibrations and to transmit sub-nanosecond delay information.

- Invention of special White Rabbit switches: As the higher resolution comes with hardware and protocol changes, special switches have been invented implementing the required changes in order to fan-out and distribute accurate timing.

- Besides the measures to increase the resolution and accuracy, the jitter is reduced by including a PLL, which will "clean" the locally syntonized clock.

Measurement results published in [17] [18] [19] showed impressive results, taking into account, that almost all functions are implemented in FPGA. It was shown, that variations of temperatures of a 5km long fiber on a spool from 12.5 centigrade to 85 centigrade resulted in phase changes below 100ps (measured between the master reference clock and slave clocks of the external PLL). Comparing the Pulse per Second (PSS) pulse generated every second by the master and slave FPGAs the variation was higher with around 450ps peak-to-peak.

Although the White Rabbit Timing System is based on industry standards, the extensions to it require significant hardware changes, which lead to the fact, that no commercial hardware like the special switch was available. But as all designs, firmware and software is provided under open hardware and open source licenses and industrial companies are interested.

#### 3.2 Bunch clock distribution system

In most circular accelerator (synchrotron) based light sources the timing relations are relatively simple. The storage ring has a defined circumference where the particle bunches require a time  $t_{ring}$  in order to complete a full turn of the ring. The period of the accelerating RF  $t_{RF}$  is required to have an integer relation to  $t_{ring}$  as

$$t_{ring} = t_{RF} * N \tag{3.3}$$

In this case N defines the number of bunches which could exist at the same time within the ring. Those places are also called buckets which could be filled with a bunch or not.

The main goal of a typical timing system for such facilities is a clock distribution system, which provides the RF reference frequency  $(1/t_{RF})$  to all end stations. At the end stations this clock will then be divided and delayed in order to generate all required signals for different applications like clock, gates or triggers for ADCs, TDC and so on. In this case the dividers and delays have to be calibrated for a certain system in order to correspond to the actual filling pattern of the ring.

In order to simplify the local divider synchronization some timing systems also allow to distribute the ring (orbit) frequency  $(1/t_{ring})$ . This is either implemented as a second distribution cable or by sending a fiducial (or data packet) on the same cable (depends on the implementation). This will be used in order to synchronize the local dividers.

The following paragraphs provide two examples of such timing systems.

#### 3.2.1 European Synchrotron Radiation Facility (ESRF)

At  $ESRF^2$  the reference frequency of 352.20MHz is generated by the master oscillator and then distributed to the end points. At the end points special devices like the BCDU8 unit are used, which allow flexible dividing and delay adjustments for multiple outputs. In special

<sup>&</sup>lt;sup>2</sup>European Synchrotron Radiation Facility, 6 rue Jules Horowitz, 38000 Grenoble, France

cases a second cable with the orbit frequency  $(1/t_{ring})$  of 355.04KHz is provided and used to synchronize the dividers of the described unit.

#### 3.2.2 PETRA III

Another example of a bunch clock distribution is used at PETRA III at DESY. This implementation provides a more integrated solution compared to the previous example, as the receiving unit includes already the divider and delay units and also special trigger outputs. The reference frequency of PETRA III is 500MHz generated by the RF master oscillator.

#### 3.3 Clock and event distribution systems

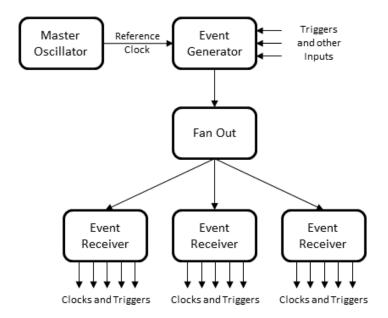

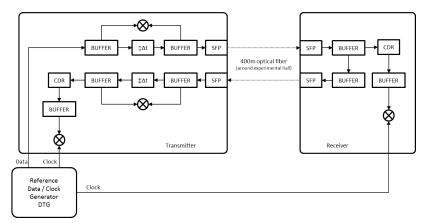

This class of timing systems is designed to distribute a reference clock (usually provided by the master RF oscillator of the accelerator) and events based on certain hardware or software conditions. The generator and transmitter of the signal are usually called event generator (EVG). In most cases the signal of an EVG is multiplied by a fan-out unit and then distributed to the event receivers (EVR). The receivers have to decode the events and recover the reference clock. The events will be converted into definable actions like providing triggers, generating interrupts, gating of signals and so on. The recovered clock, fractions of it (generated via dividers) or gated versions will be provided at the output. Figure 3.4 illustrates the general system layout.

Figure 3.4: Overview of a general event based timing system. The event generator is connected to the master oscillator providing the reference. External triggers define the basis for events. The event stream is generated and distributed via a fan-out to multiple event receivers. They decode the events and provide clocks and triggers to local applications.

Those systems, as used at different facilities, do not have (or do not utilize) a feedback channel in order to measure and compensate for any cable delay or drift. For those systems it is assumed, that drifts are slow enough to not violate the defined requirements for the application, and initial delays will be calibrated via user definable delays or cable length adjustments. The following paragraphs will present some implementations of this type of timing system.

#### 3.3.1 FLASH Event System

The event system installed at the Free Electron Laser in Hamburg (FLASH) at DESY implements an event and clock distribution based timing system.

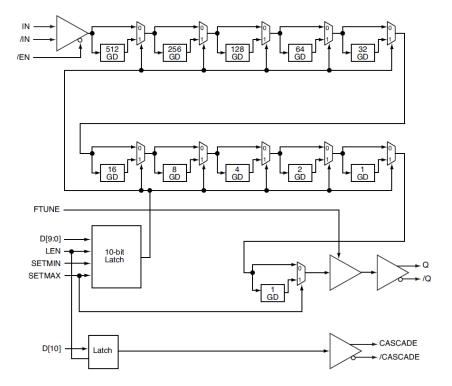

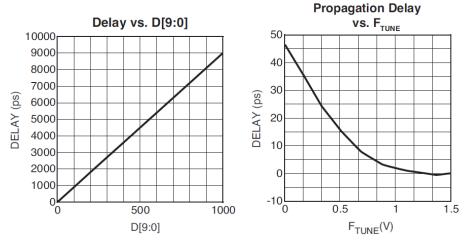

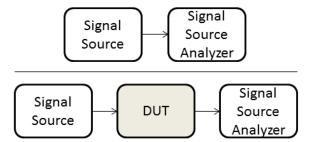

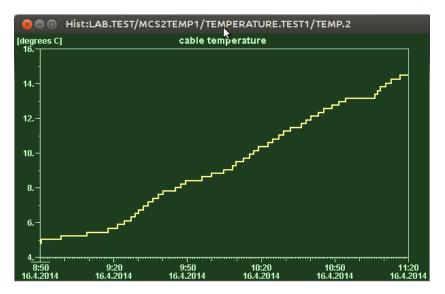

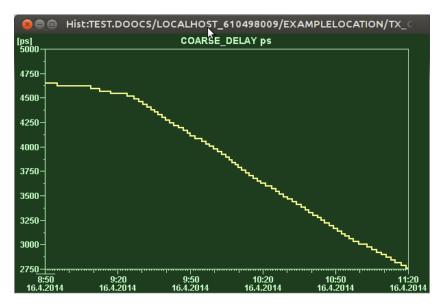

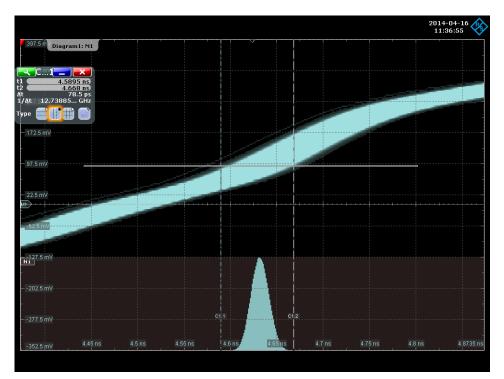

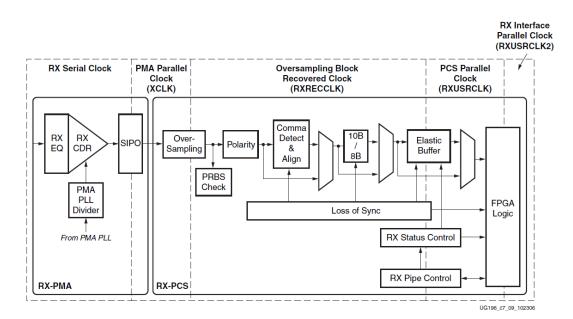

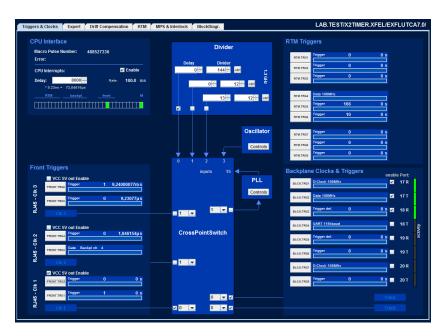

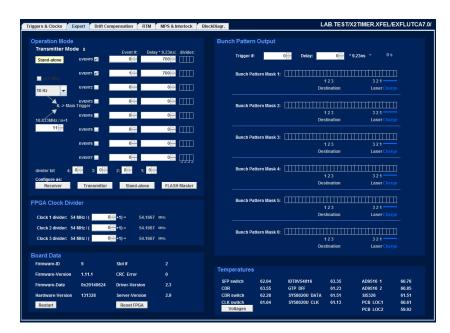

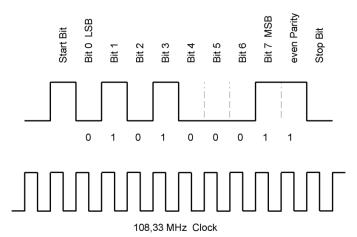

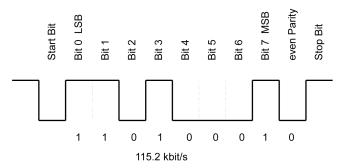

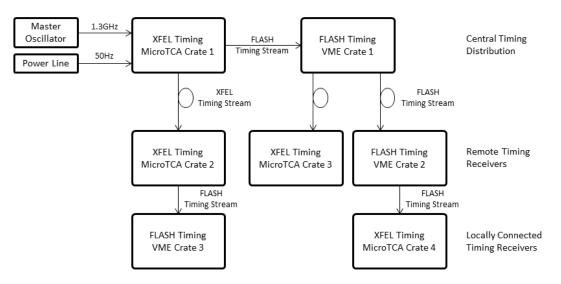

The EVG provides inputs for its reference clock (approx. 9MHz), a cycle pulse, which is derived from the 50Hz (or 60Hz) mains frequency as well as external trigger inputs. Based on the derived external cycle pulse (usually 10Hz), external triggers and relative to those via firmware defined points in time, the events are generated and encoded into a data stream. The events are 8-bit words defining up to 256 events. For signal transmission and line encoding the Manchester code [20] is used, where the bit rate is based on the provided reference clock. Transmission to the EVR is possible directly (via fan-out transmitter modules with coaxial cables or multi-mode fibers) and via daisy-chaining of modules, where intermediate EVR act also as repeaters.