# Development, Validation, and Application of Semi-Analytical Interconnect Models for Efficient Simulation of Multilayer Substrates

Vom Promotionsausschuss der

Technischen Universität Hamburg-Harburg

zur Erlangung des akademischen Grades

Doktor-Ingenieur (Dr.-Ing.)

genehmigte Dissertation

von Renato Rimolo-Donadio

aus

San José, Costa Rica

1. Gutachter:

Prof. Dr. sc. techn. Christian Schuster

2. Gutachter:

Prof. Dr.-Ing. Arne Jacob

3. zusätzlicher Gutachter:

Dr. Xiaoxiong Gu (IBM T. J. Watson Research Center, NY, USA)

Vorsitzender des Promotionsverfahrens:

Prof. Dr. Ernst Brinkmeyer

Tag der mündlichen Prüfung: 17.12.2010

About the illustration: Urban Interconnects by R. Rimolo-Donadio, Acrylic on wood, 2002.

#### Abstract

This thesis deals with the efficient modeling and simulation of multilayer substrates in high-speed electronic systems, such as packages and printed circuit boards.

Semi-analytical models for the electrical behavior of vias and traces are presented and a framework for automated simulation of multilayer structures is proposed. The models are devised in terms of microwave network parameters and they rely on the formulation of the parallel-plate impedance to describe wave propagation between adjacent reference planes. Via-to-plane capacitances are used to approximate the near fields around via barrels. A modal decomposition method allows the merging of parallel-plate and trace models; microwave segmentation techniques are applied to solve multilayer configurations.

An extensive and thorough validation of the models is presented, using general-purpose numerical methods for electromagnetic simulation and hardware measurements. The validation cases include multilayer via configurations with power and ground vias, mixed reference planes, single-ended links, differential links, and via arrays. The numerical efficiency, advantages and disadvantages of the proposed approach are covered in the discussion.

Several application scenarios of realistic complexity are also evaluated. Studies of differential links between ball grid arrays, stub via resonances, and differential to common-mode conversion are presented. The utilization of the models for co-simulation of power and signal integrity is demonstrated as well as the extension of the method to handle arbitrarily shaped plates and radiated emissions. It is shown that the models can provide good results up to 40 GHz and a numerical efficiency of at least two orders of magnitude better than general-purpose numerical methods for electromagnetic simulation.

Author key-words: modal decomposition, printed circuit board, package, parallel plates, power integrity, signal integrity, traces, via.

## Acknowledgment

This thesis was the result of three and a half years of work at the Institute of Electromagnetic Theory (TET) of the Technical University of Hamburg-Harburg (TUHH), between November 2006 and May 2010, with a research position funded by TUHH. Along this time several people and organizations have contributed in different ways to the completion of this work.

I would like to express my sincere gratitude to Prof. Dr. Christian Schuster, for giving me the opportunity of carrying out this work, and for the dedicated guidance and advice. I was lucky of having an extraordinary person and scientist as supervisor. His motivation, high principles, and commitment to the research and academic activities have been the model to follow during all this time. I would also like to thank Prof. Dr. Arne Jacob, second examiner, and to Prof. Dr. Ernst Brinkmeyer, president of the Doctoral Committee evaluating this thesis, for the careful revision and evaluation of this work.

My gratitude goes to Dr. Xiaoxiong (Kevin) Gu, who was also external examiner of this work. His support and feedback along the different phases of this project have been essential for its successful completion. I would also like to thank Dr. Young H. Kwark, for his mentorship, support, and all the valuable feedback provided during these years. My gratitude is extensive to Dr. Mark B. Ritter, M. S. Christian Baks, and the other members of the former High-Speed I/O Subsystems and Packaging Group at the IBM T. J. Watson Research Center, Yorktown Heights, New York, USA, who have cooperated a lot with our research and provided the hardware and measurements used in this work. I also had a great and productive stay with them at IBM during the summer 2007.

This work would not be possible without the help of Dr.-Ing. Heinz-Dietrich Brüns. His contributions to the research activities, careful analysis of the work, and feedback have been crucial for the development of this project. I would also like to express my gratitude to all the colleagues and staff at the Institute of Electromagnetic Theory for their support. Special thanks to my colleagues Dipl.-Ing. Miroslav Kotzev, M.Sc. Xiaomin Duan, and Dipl.-Ing. Sebastian Müller, for their help and the great team work. Thanks go also to the students who contributed with their final works to our research activities.

iv Acknowledgment

The discussions with the people involved in the IBM/ Missouri University of Science and Technology (MST)/ University of L'Aquila/ TUHH weekly meetings have been also very important for the progress of this work. My appreciation goes to all them, in particular to Dr. Bruce Archambeault, at IBM USA, Prof. Dr. James L. Drewniak, Prof. Dr. Jun Fan, Dr. Yao-Jiang Zhang, Prof. Dr. Albert Ruehli, and their research team at the Electromagnetic Compatibility Group, MST (former University of Missouri-Rolla), USA, for all their cooperation and feedback.

Finally, I would like to thank to my family and friends. I am indebted to my wife Karolina and our son Leonardo, my parents Roque and Olga, and my sister Fiorella for their unconditional support. This thesis is for them.

# Contents

| List of Figures and Tables                                | ix |

|-----------------------------------------------------------|----|

| List of Symbols and Acronyms                              | xv |

| 1. Introduction                                           | 1  |

| 1.1. Motivation and Context of this Work                  | 1  |

| 1.2. Organization of the Work                             | 2  |

| 1.3. Conference and Journal Contributions                 | 4  |

| 2. Multilayer Substrates in High-Speed Electronic Systems | 5  |

| 2.1. Multilayer Substrate Technologies                    | 5  |

| 2.2. Signal Integrity                                     | 9  |

| 2.3. Power Integrity                                      | 10 |

| 2.4. Electromagnetic Compatibility                        | 12 |

| 2.5. Overview of Techniques                               |    |

| for High-Frequency Modeling of Multilayer Substrates      | 13 |

| 3. Physical Effects Associated with Vias                  | 15 |

| 3.1. Types of Signal Vias                                 | 15 |

| 3.2. Excitation of Parallel-Plate Modes                   | 16 |

| 3.3. Effect of Ground Vias (Return Vias)                  | 22 |

| 3.4. Via Crosstalk                                        | 25 |

| 3.5. Transmission Line Parameters of Via Interconnects    | 27 |

| 3.6. The Via Stub Effect                                  | 33 |

vi

| 4. De | evelopment of Semi-Analytical Via and Trace Models                    | $\dots 37$ |

|-------|-----------------------------------------------------------------------|------------|

|       | 4.1. Modeling Approach                                                | 37         |

|       | 4.2. Via Model and Its Formulation using Microwave Network Parameters | 39         |

|       | 4.3. Analytical Computation of the Parallel-Plate Impedance           | 41         |

|       | 4.3.1. The Cavity Resonator Method                                    | 42         |

|       | 4.3.2. The Radial Waveguide Method                                    | 45         |

|       | 4.3.3. Comparison of Convergence Properties                           |            |

|       | and Computational Efficiency of the Methods                           | 47         |

|       | 4.3.4. Hybridization of Methods                                       | 50         |

|       | 4.3.5. Limitations of Analytical Formulations and Outlook             | 53         |

|       | 4.4. Computation of Via-to-Plane Capacitances                         | 54         |

|       | 4.5. Modeling of Power and Ground Vias                                | 56         |

|       | 4.6. Extended Model for Vias and Traces                               | 57         |

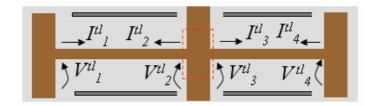

|       | 4.6.1. Modal Decomposition                                            | 59         |

|       | 4.6.2. Via Model Including Stripline Transitions                      | 62         |

|       | 4.7. Generalized Method for Simulation of Multilayer Substrates       | 66         |

| 5. Va | didation of the Models                                                |            |

| wi    | th Full-Wave Simulations and Measurements                             | 71         |

|       | 5.1. Multilayer Vias                                                  | 71         |

|       | 5.2. Single-Ended Links                                               | 75         |

|       | 5.2.1. Validation of the Via and Trace Model                          | 75         |

|       | 5.2.2. Simulation of Single-Ended Links                               |            |

|       | and Correlation to Full-Wave Simulations                              | 79         |

|       | 5.2.3. Effect of Ground Vias                                          | 83         |

|       | 5.2.4. Mixed Reference Power/Ground Planes                            | 83         |

|       | 5.2.5. Blind and Buried Vias                                          | 86         |

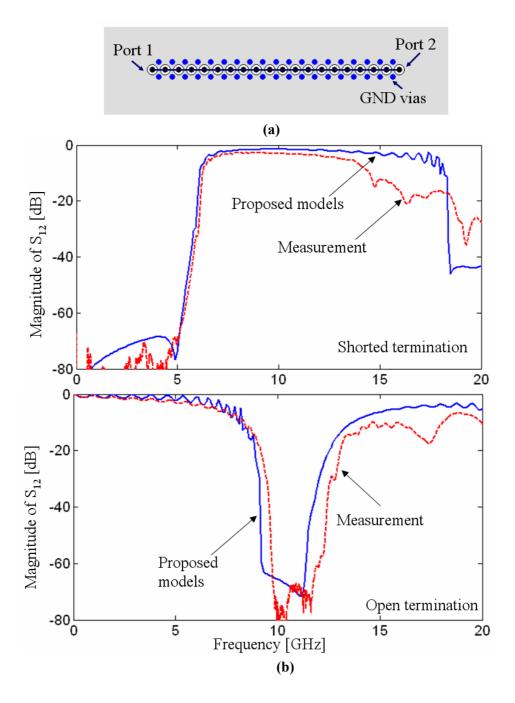

|       | 5.2.6. Model-to-Hardware Correlation                                  | 87         |

Contents

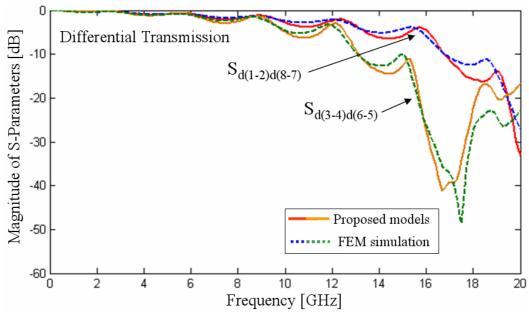

| 5.3. Differential Links                                                      | 92  |

|------------------------------------------------------------------------------|-----|

| 5.3.1. Simulation of Coupled Striplines                                      | 93  |

| 5.3.2. Model-to-Hardware Correlation                                         | 94  |

| 5.4. Via Arrays                                                              | 98  |

| 5.5. Model Efficiency                                                        | 103 |

| 5.6. Model Limitations and Outlook                                           | 107 |

| 6. Application of the Models to SI, PI, and EMI Analyses                     | 111 |

| 6.1. Application to Signal Integrity Analysis                                | 111 |

| 6.1.1. Simulation of Differential Links across BGA Via Arrays                | 112 |

| 6.1.2. Simulation of Via Stub Resonances                                     | 119 |

| 6.1.3. Simulation of Mode Conversion in Differential Links                   | 125 |

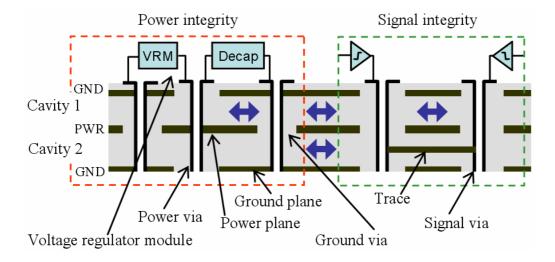

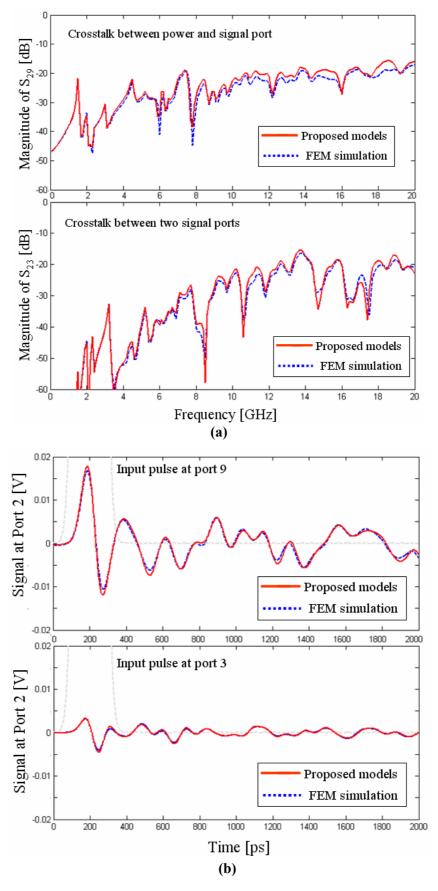

| 6.2. Application to Combined Signal and Power Integrity Analysis             | 132 |

| 6.2.1. Simulation of the Interaction between Signal and Power Vias.          | 133 |

| 6.2.2. Simulation of Structures with Decoupling Capacitors                   | 136 |

| 6.3. Application to Combined                                                 |     |

| Signal and Power Integrity, and Radiated Emissions Analysis                  | 141 |

| 6.3.1. Extension of the Method                                               |     |

| for Analysis of Multilayer Printed Circuit Boards                            | 142 |

| 6.3.2. Application Example                                                   | 147 |

| 7. Conclusions and Outlook                                                   | 153 |

| A. Mathematical Appendix                                                     | 157 |

| A.1. Bandwidth of Digital Signals                                            | 157 |

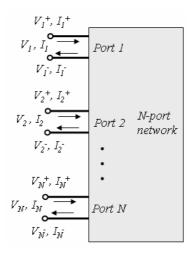

| A.2. Microwave Network Parameters                                            | 159 |

| A.3. Via Model Matrix Expansion                                              | 162 |

| A.4. Derivation of the Radial Waveguide Formula to Compute $\mathbf{Z}^{pp}$ | 163 |

| A.5. Derivation of the Modal Transformation Matrices                         | 165 |

| A.6. Formulation of the Via-Stripline Model                                  | 168 |

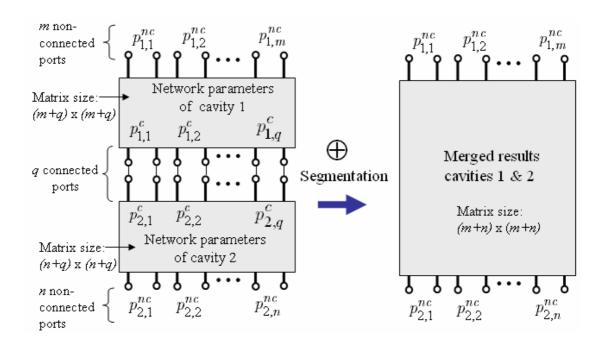

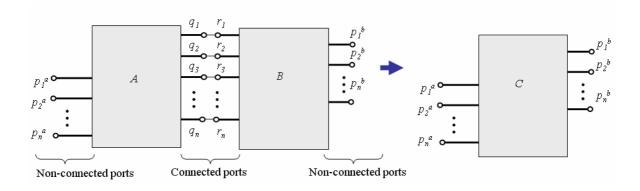

| A.7. Segmentation Techniques                                                 | 170 |

viii Contents

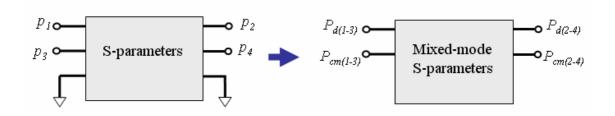

| A.8. Mixed-Mode S-Parameters                                | 172 |

|-------------------------------------------------------------|-----|

| A.9. The Contour Integral Method (CIM)                      | 174 |

| A.10. The Equivalence Principle                             | 176 |

| B. Code Architecture                                        | 177 |

| C. Additional Results                                       | 179 |

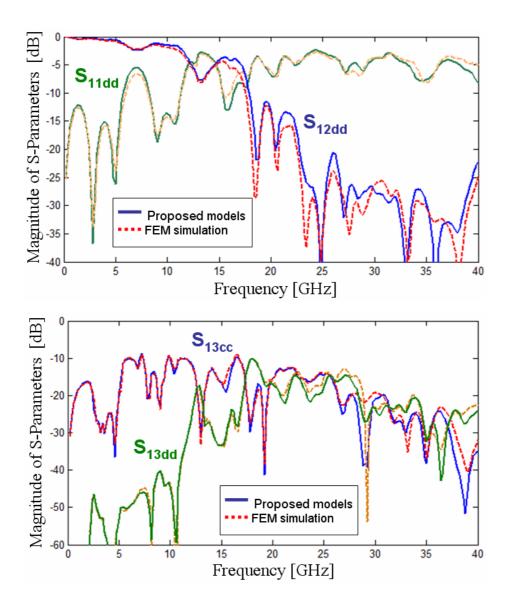

| C.1. Results up to 40 GHz for the Examples in Section 5.2.6 | 179 |

| C.2. Results up to 40 GHz for the Example in Section 5.3.2  | 181 |

| References                                                  | 183 |

| Curriculum Vitae                                            | 197 |

# List of Figures and Tables

# Figures

| Figure 1.1 Some high-speed standards for digital-systems and their maximal data rates $\dots$ 2 |

|-------------------------------------------------------------------------------------------------|

| Figure 2.1 Utilization of optical and electrical links                                          |

| Figure 2.2 Illustration of interconnect levels in high-speed electronic systems                 |

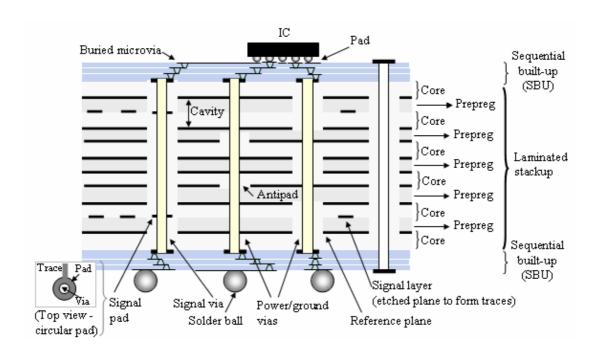

| Figure 2.3 Diagram of a multilayer substrate                                                    |

| combining a laminated core with sequential built-up layers                                      |

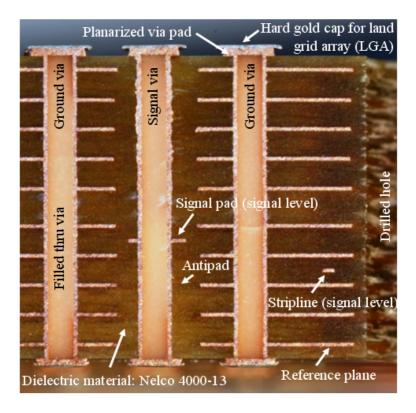

| Figure 2.4 Multilayer printed circuit board cross section                                       |

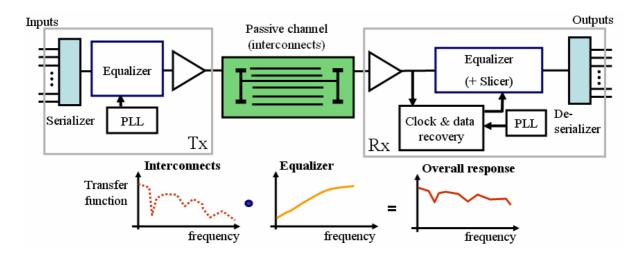

| Figure 2.5 Simplified diagram of a high-speed serial link                                       |

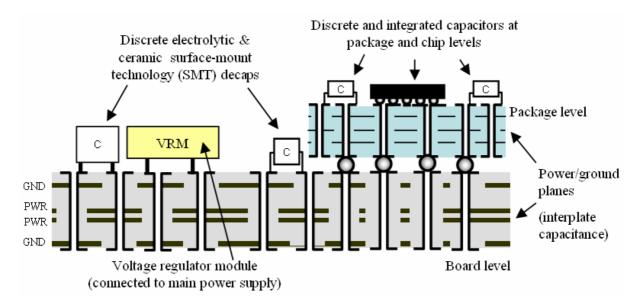

| Figure 2.6 Diagram of a power distribution                                                      |

| network main components at board and package levels                                             |

| Figure 2.7 General classification of available methods                                          |

| for high-frequency modeling of multilayer substrates                                            |

| Figure 3.1 Common via types used in multilayer substrates                                       |

| Figure 3.2 Illustration of parallel-plate modes excited by via transitions                      |

| Figure 3.3 Example of a multilayer via                                                          |

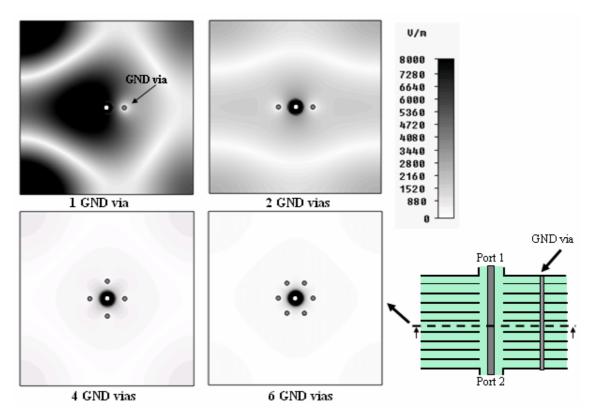

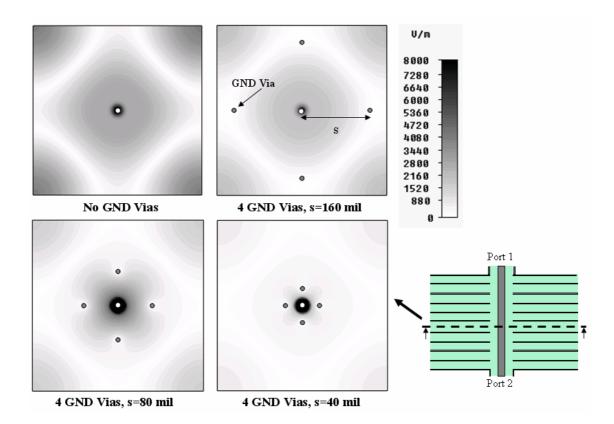

| Figure 3.4 Magnitude of the electric field inside the fifth cavity (PML)                        |

| Figure 3.5 Magnitude of the electric field inside the fifth cavity (PMC)                        |

| Figure 3.6 Impedance parameters for the via configuration in Figure 3.3                         |

| Figure 3.7 Simulated reflection and transmission for the multilayer via                         |

| Figure 3.8 Magnitude of the electric field complex amplitude inside the fifth cavity            |

| at 16 GHz, considering a different number of ground vias and PMC boundaries                     |

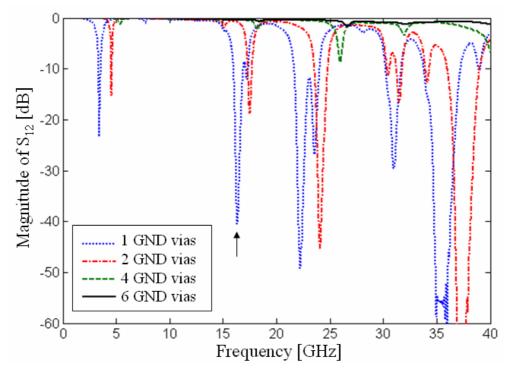

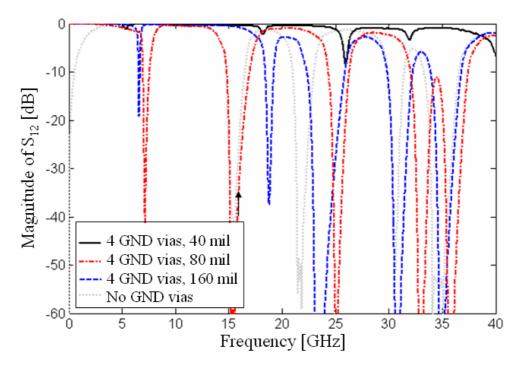

| Figure 3.9 Transmission over a signal via using a different number of ground vias               |

| Figure 3.10 Magnitude of the electric field complex magnitude inside the fifth cavity           |

| at 16 GHz, for one signal and four ground vias placed at different radial separations 24        |

| Figure 3.11 Transmission over a signal via using four ground vias                           | 24   |

|---------------------------------------------------------------------------------------------|------|

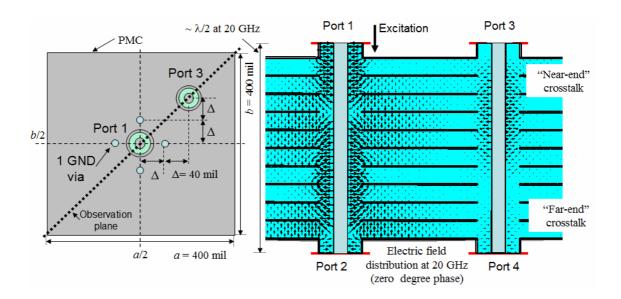

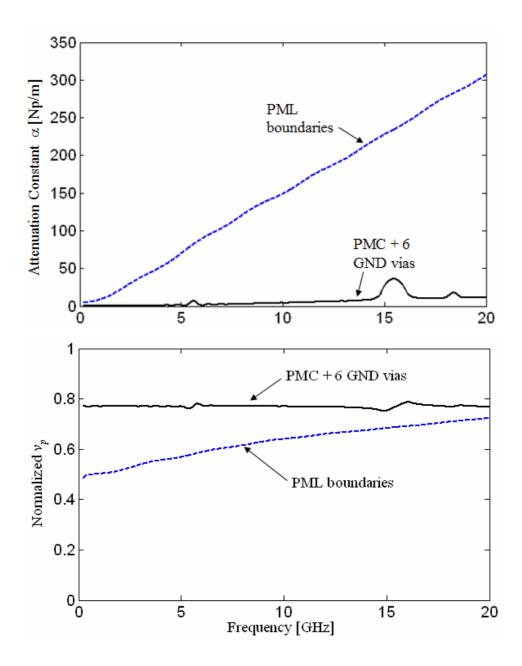

| Figure 3.12 FIT simulation of crosstalk among two vias crossing a 10-cavity stackup         | 25   |

| Figure 3.13 Near-end and far-end crosstalk for the configuration in Figure 3.12             | 26   |

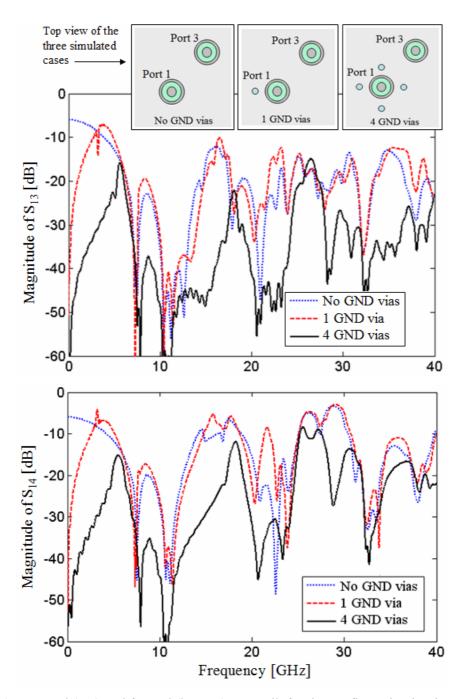

| Figure 3.14 Via impedance for different                                                     |      |

| boundary conditions at the board edges, and in presence of ground vias                      | . 28 |

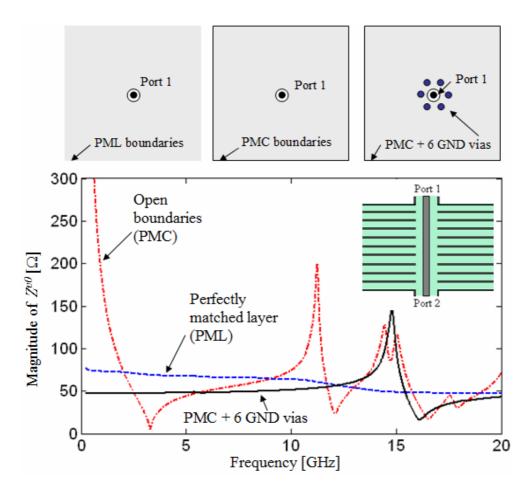

| Figure 3.15 Attenuation constant and normalized propagation                                 |      |

| velocity for the cases of absorbing and open boundaries with six ground vias                | 29   |

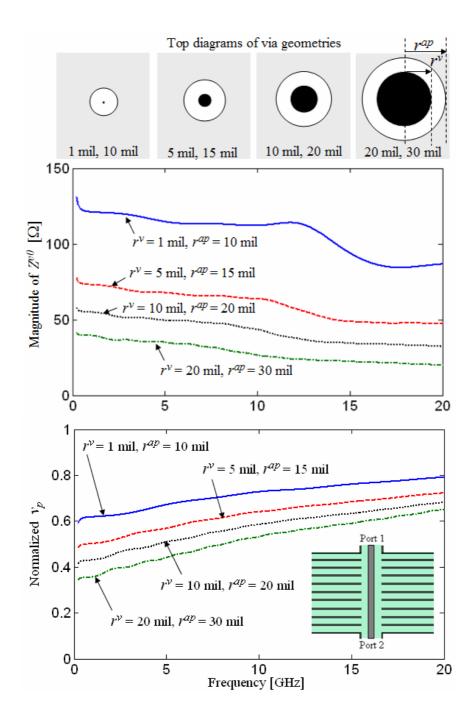

| Figure 3.16 Impedance and propagation velocity of a single via for different sizes          | 30   |

| Figure 3.17 Via impedance and                                                               |      |

| propagation velocity of a single via for different antipad sizes                            | 31   |

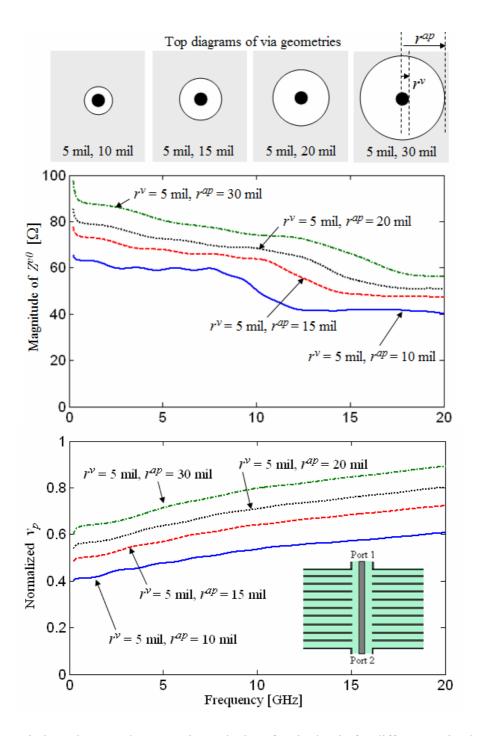

| Figure 3.18 Via impedance and transmission for different cavity thicknesses                 | 32   |

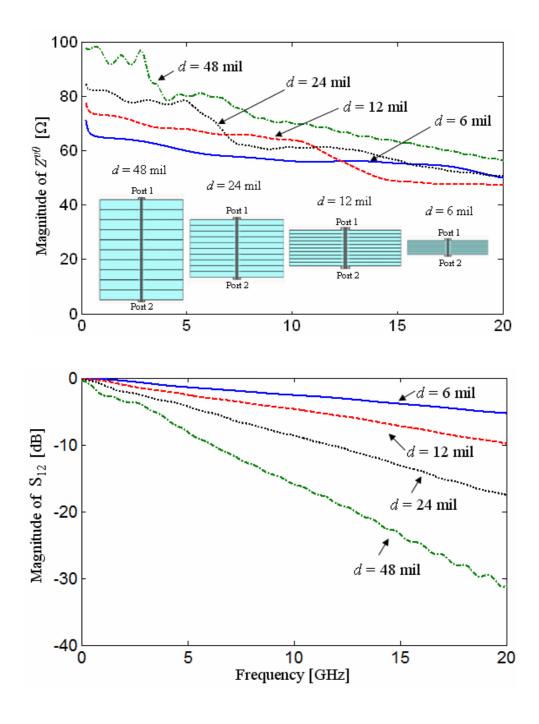

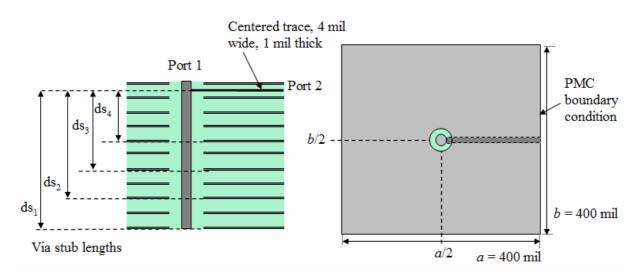

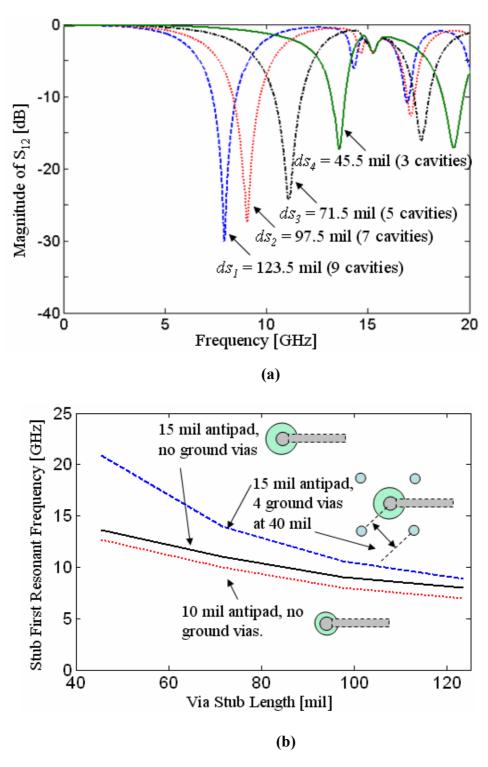

| Figure 3.19 Description of the structure for simulation of the via stub effect              | . 34 |

| Figure 3.20 Simulation of the via stub effect                                               | . 35 |

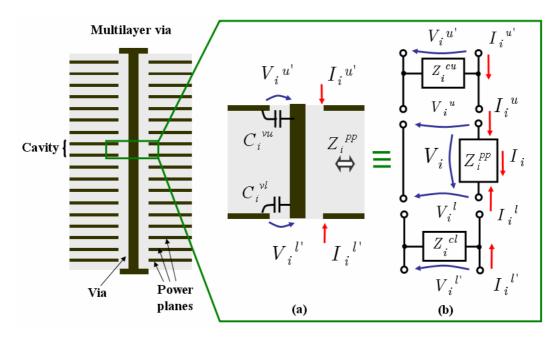

| Figure 4.1 Description of the via model for a single via                                    | 40   |

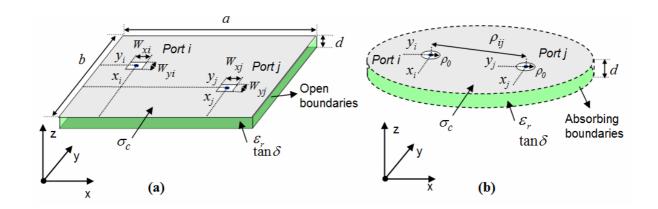

| Figure 4.2 Diagrams of the parallel-plate impedance $(\mathbb{Z}^{pp})$ calculation domains | . 42 |

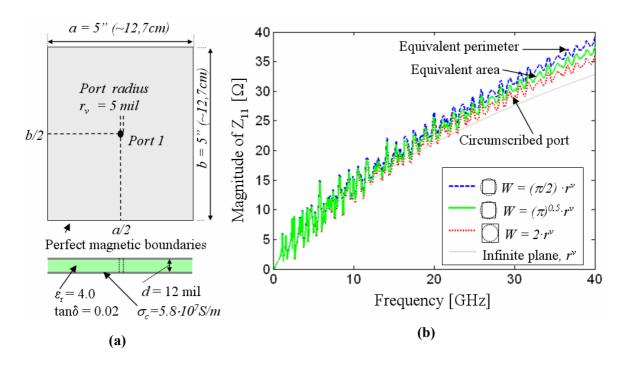

| Figure 4.3 Effect of port approximation for                                                 |      |

| circular geometries in the cavity resonator model                                           | . 44 |

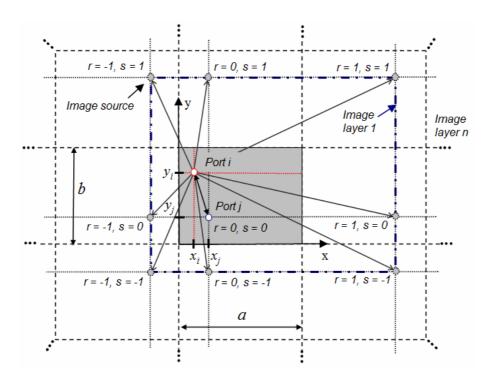

| Figure 4.4 Radial waveguide approach combined with                                          |      |

| image theory to compute the parallel-plate impedance of finite rectangular plates           | . 46 |

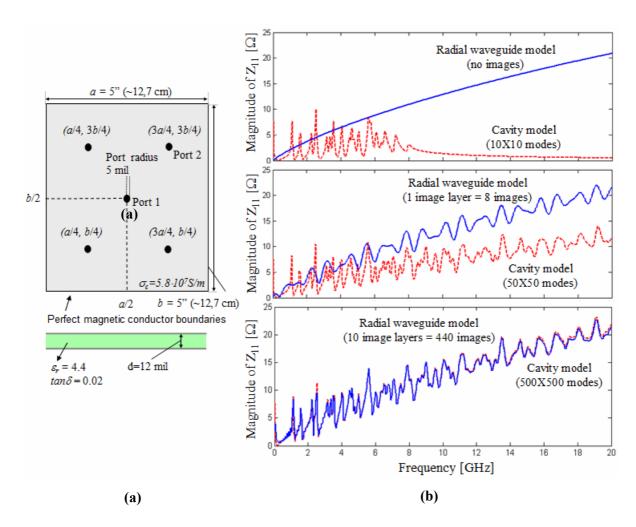

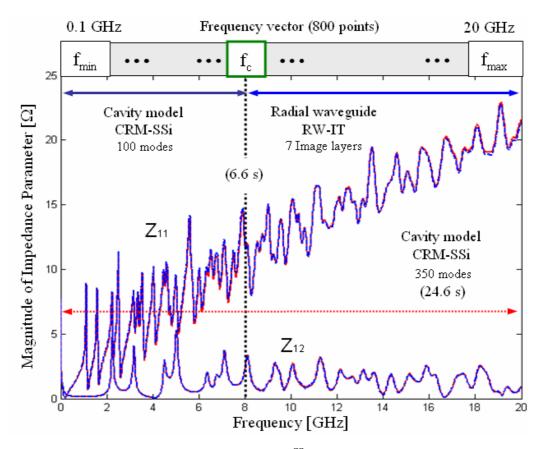

| Figure 4.5 Comparison of the convergence of the methods to compute $Z^{pp}$                 | 48   |

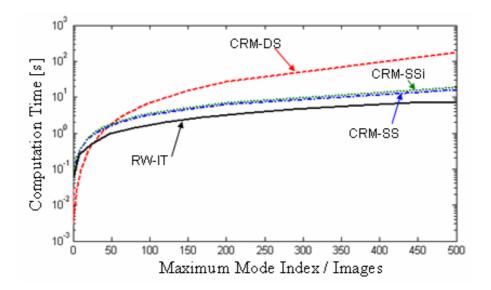

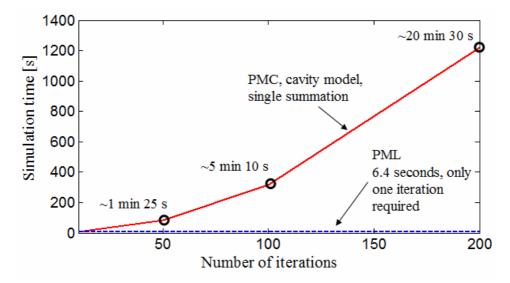

| Figure 4.6 Computation time as a function of the number                                     |      |

| of iterations for the cavity resonator model and the radial waveguide method                | 49   |

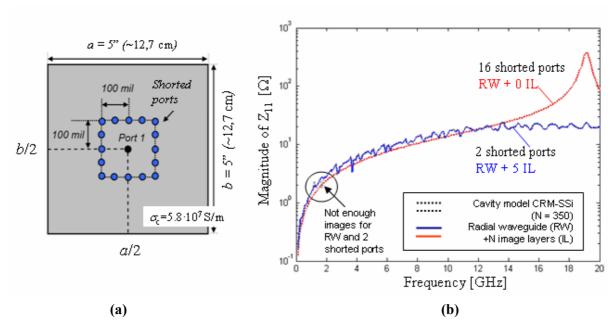

| Figure 4.7 Input impedance as a function of the number of shorted ports                     | . 50 |

| Figure 4.8 Hybridization of methods to compute $\mathbb{Z}^{pp}$                            | . 51 |

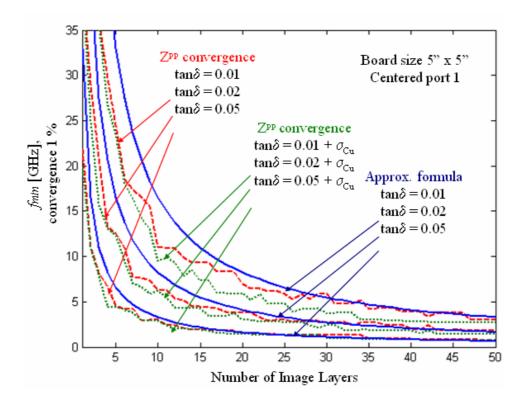

| Figure 4.9 Minimum converged frequency as a function of the number of image layers          | . 52 |

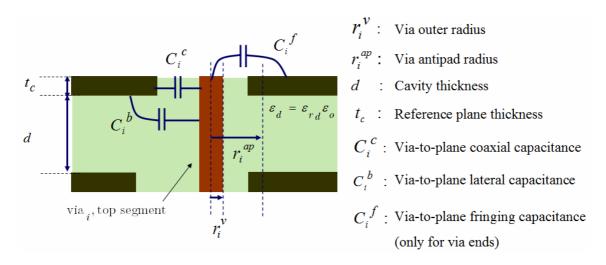

| Figure 4.10 Definition of via-to-plane capacitances                                         | . 55 |

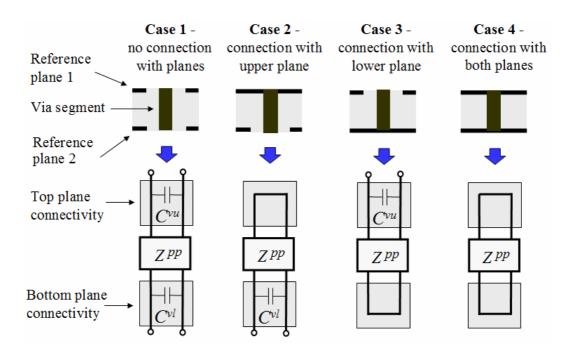

| Figure 4.11 Via connectivity with respect to the reference planes for a single cavity       | 57   |

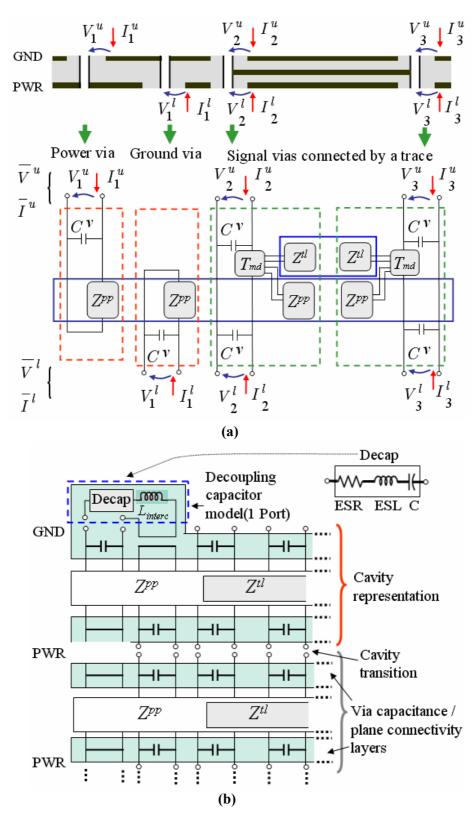

| Figure 4.12 Approach used to model multilayer                                               |      |

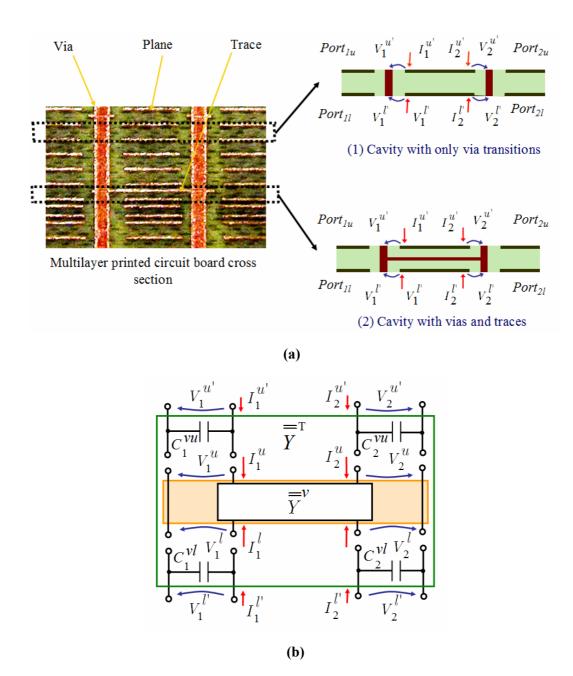

| board structures with vias and internal traces connecting vias                              | 58   |

| Figure 4.13 Illustration of the modal                                                       |      |

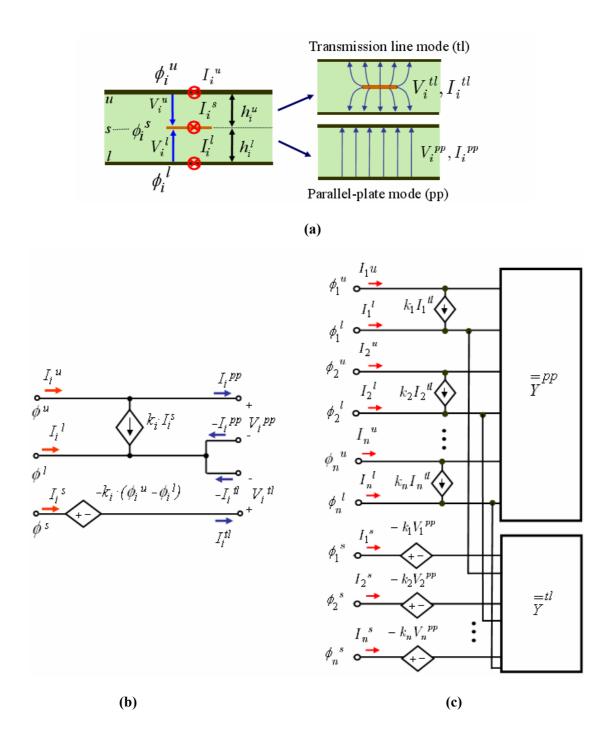

| decomposition approach applied to model vias connected by traces                            | . 61 |

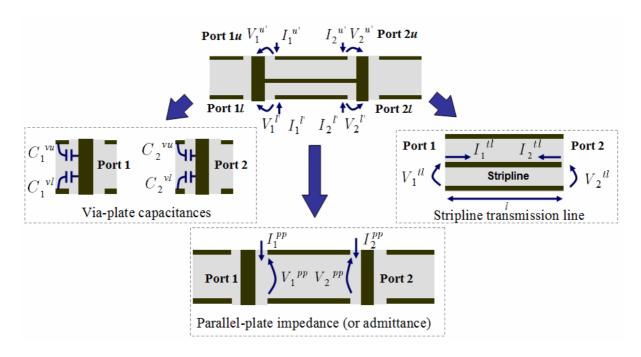

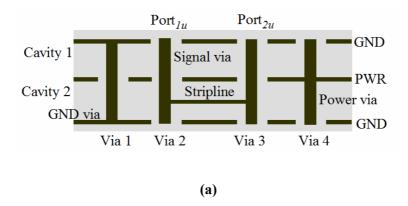

| Figure 4.14 Example of two vias connected by a centered stripline                         | 4 |

|-------------------------------------------------------------------------------------------|---|

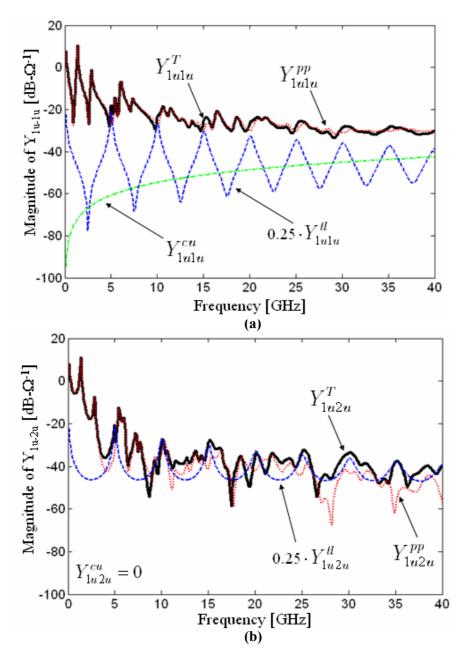

| Figure 4.15 Contribution of model components for the case shown in Figure 4.14            | 5 |

| Figure 4.16 Concatenation of partial cavity results by using segmentation                 | 7 |

| Figure 4.17 Partitioning approach to model multilayer structures                          | 8 |

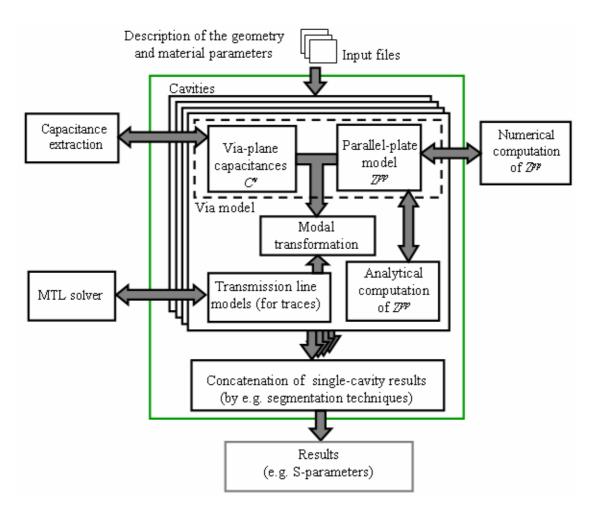

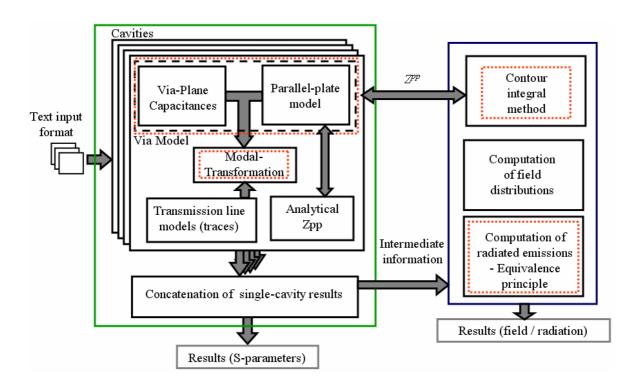

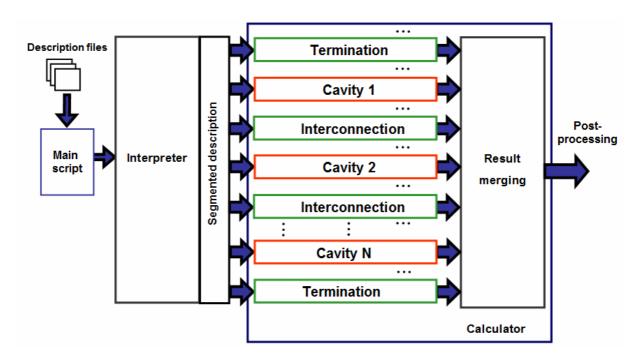

| Figure 4.18 Functional block diagram                                                      |   |

| of the modelling approach for simulation of multilayer substrates 69                      | 9 |

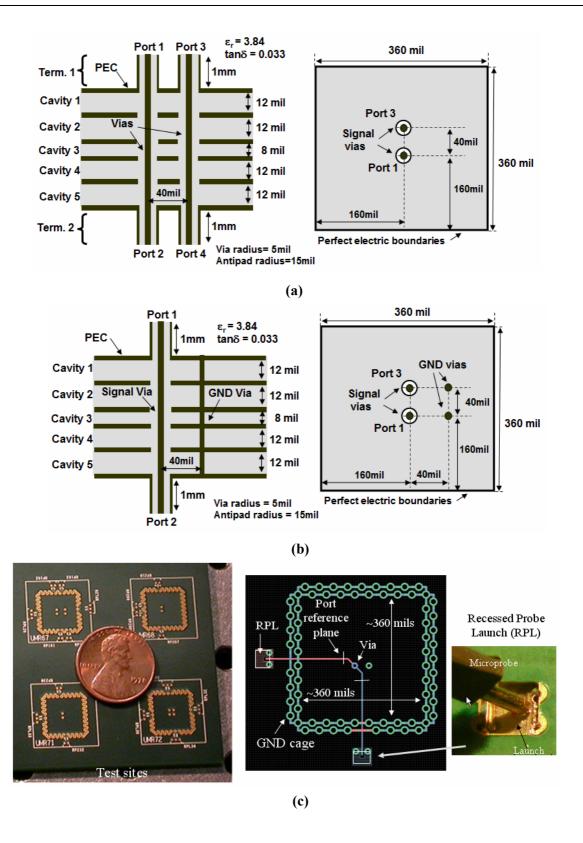

| Figure 5.1 Multilayer via modeling examples                                               | 2 |

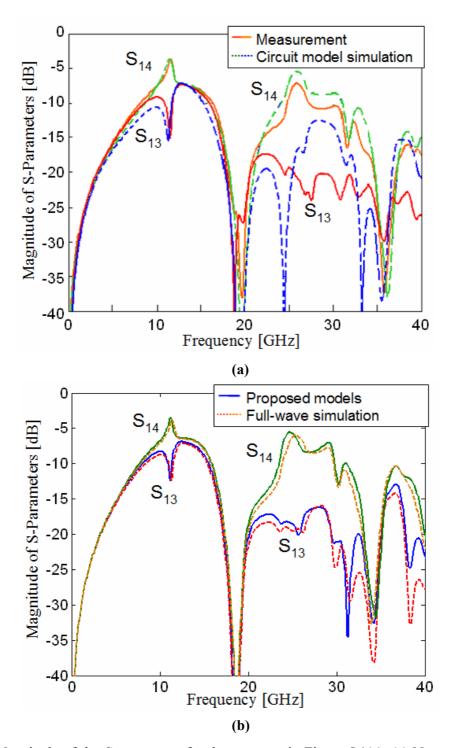

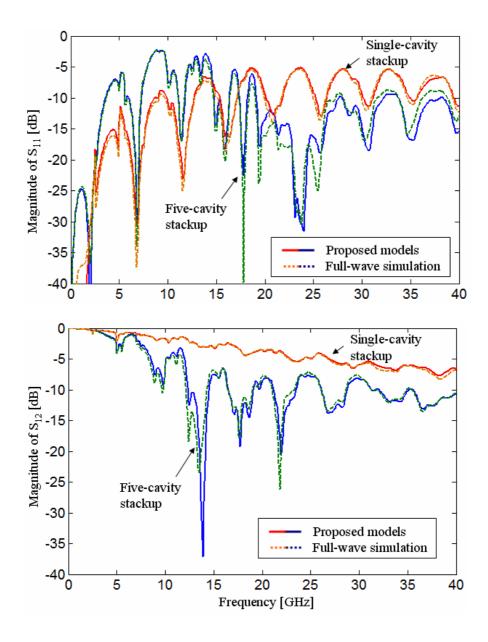

| Figure 5.2 Magnitude of $S$ -parameters for the structure in Figure 5.1(a)                | 3 |

| Figure 5.3 Magnitude of $S$ -parameters for the structure in Figure 5.1(b)                | 4 |

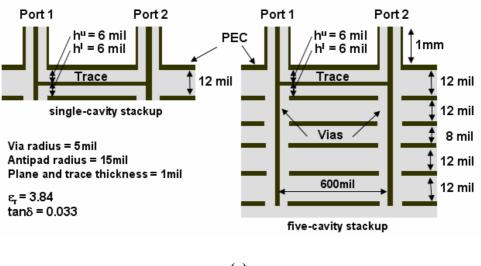

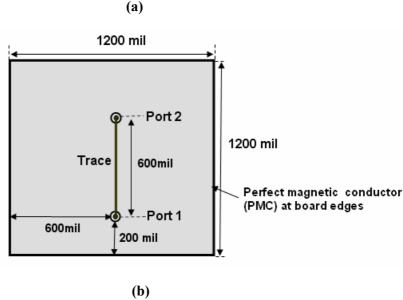

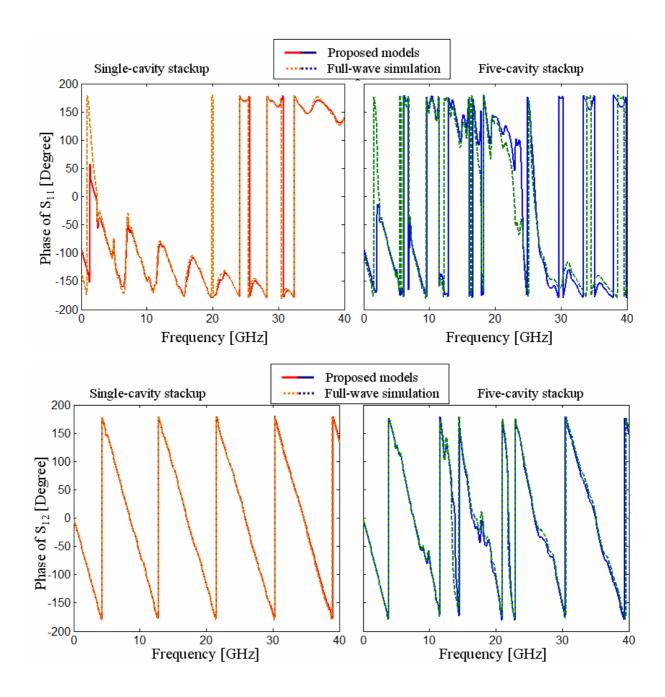

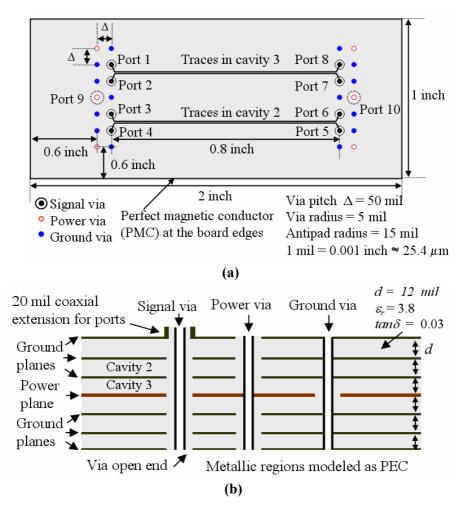

| Figure 5.4 Structure for validation of the via and trace model                            | 3 |

| Figure 5.5 Magnitude of the $S$ -parameters                                               |   |

| for the evaluation case of two vias connected by a trace (Figure 5.4)                     | 7 |

| Figure 5.6 Phase of the $S$ -parameters for                                               |   |

| the evaluation case of two vias connected by a trace (Figure 5.4)                         | 8 |

| Figure 5.7 Test case used to validate the model against full-wave methods                 | ) |

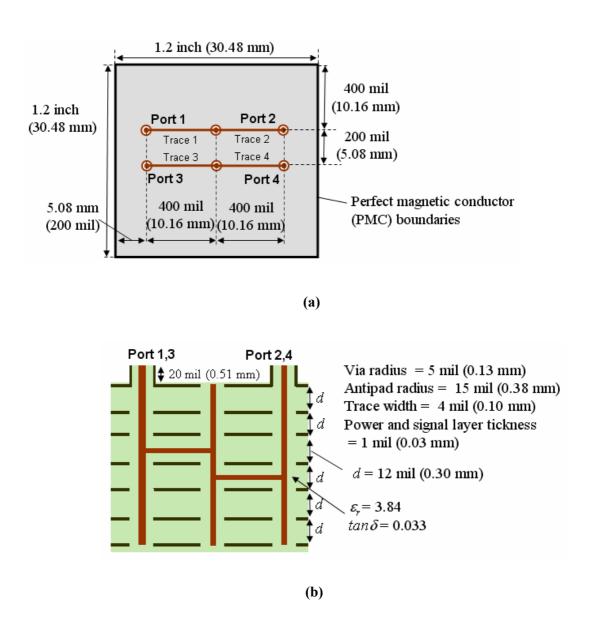

| Figure 5.8 Magnitude of S-parameters for the structure in Figure 5.7                      | 1 |

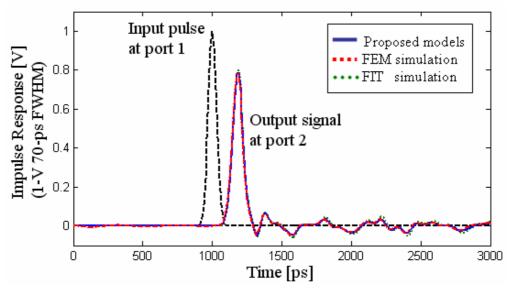

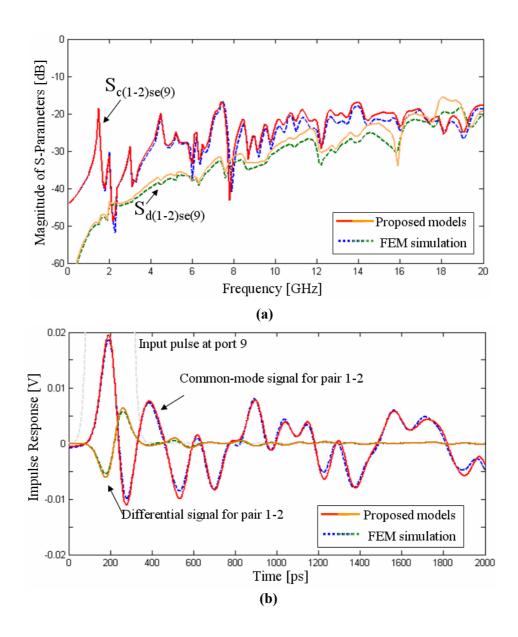

| Figure 5.9 Impulse response computed for the structure in Figure 5.7                      | 2 |

| Figure 5.10 Contribution of via-to-plane capacitances to the total model results          | 2 |

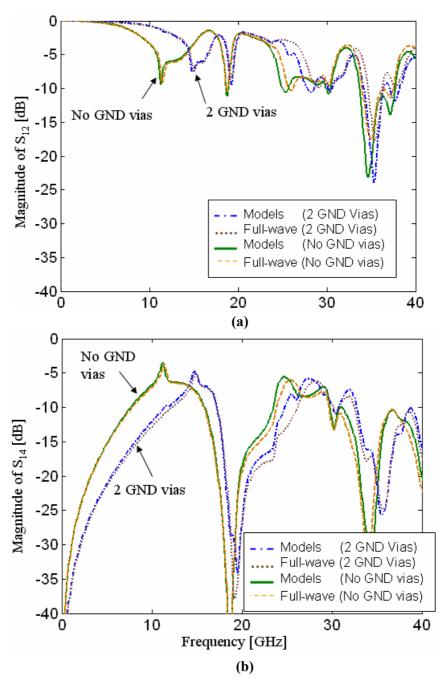

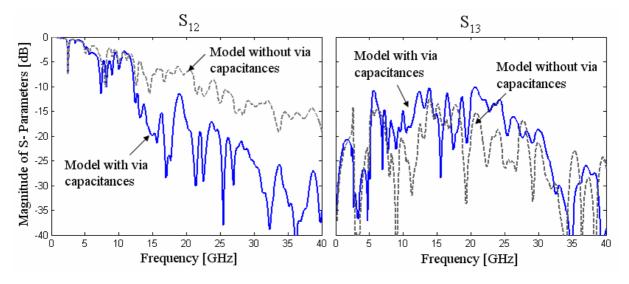

| Figure 5.11 Test cases with ground vias                                                   | 4 |

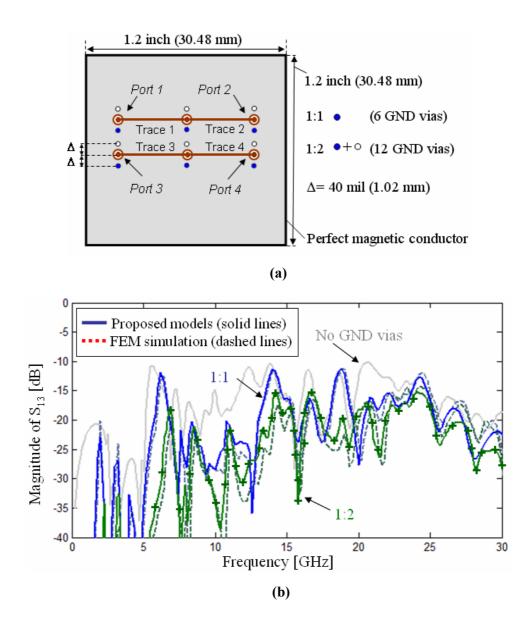

| Figure 5.12 Test cases with and without mixed reference planes                            | 5 |

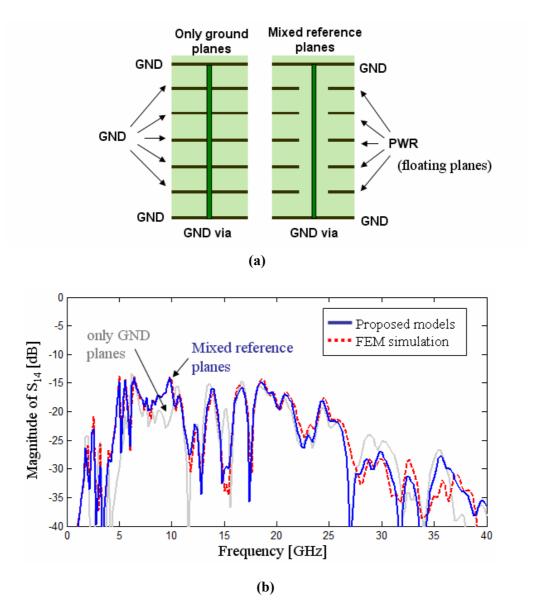

| Figure 5.13 Cross section diagram of the modified test structure, replacing               |   |

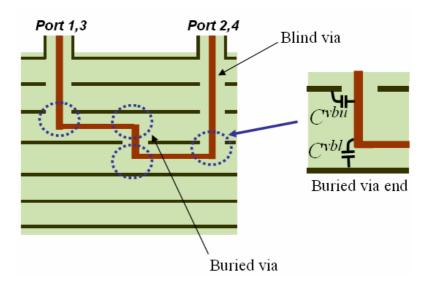

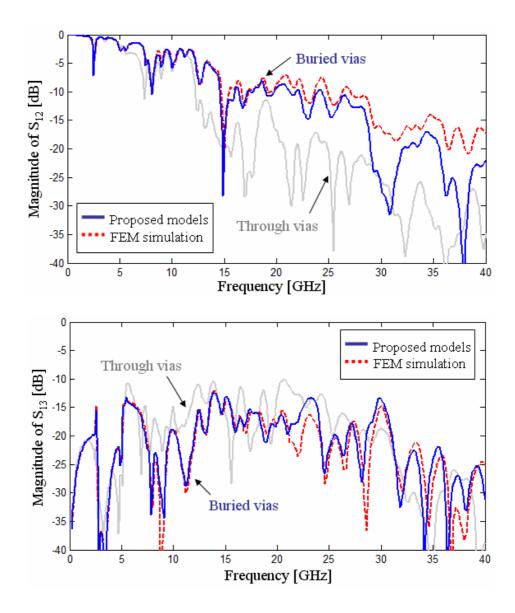

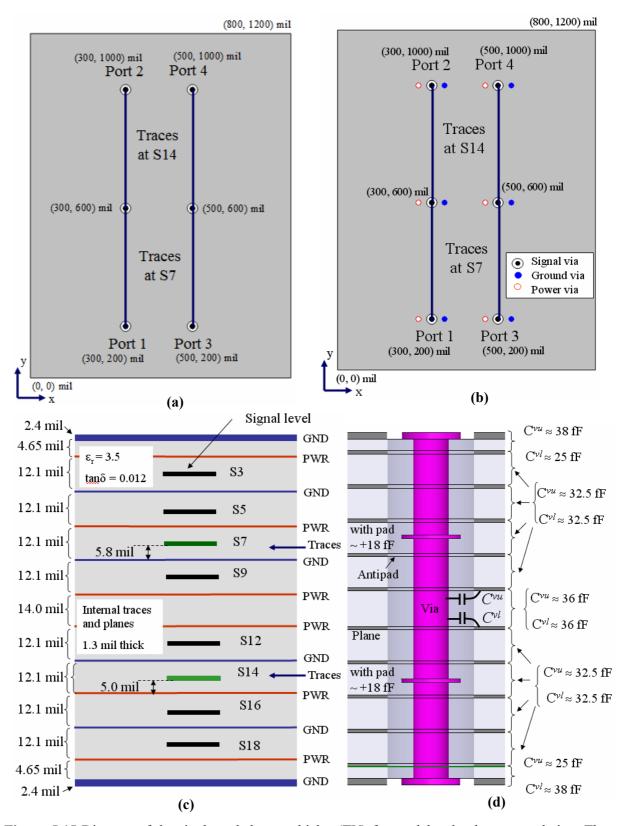

| through-hole signal vias in the structure of Figure 5.7 with blind or buried vias         | 6 |

| Figure 5.14 Transmission and near-end crosstalk                                           |   |

| for the configuration with blind and buried vias in Figure 5.13                           | 7 |

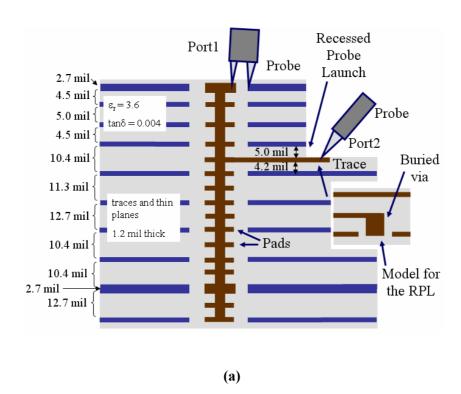

| Figure 5.15 Diagram of the single-ended test vehicles for model-to-hardware correlation 8 | 8 |

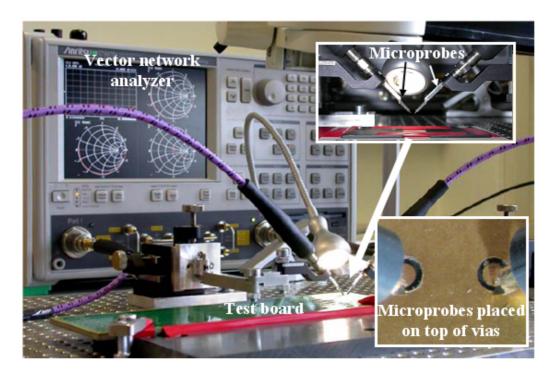

| Figure 5.16 Typical measurement setup for PCB structures in the GHz range                 | ) |

| Figure 5.17 Magnitude of S-parameters for the TV-1 in Figure 5.15                         | ) |

| Figure 5.18 Magnitude of S-parameters for the TV-2 in Figure 5.15                         | 1 |

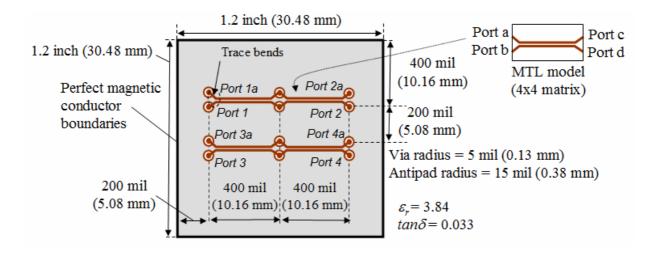

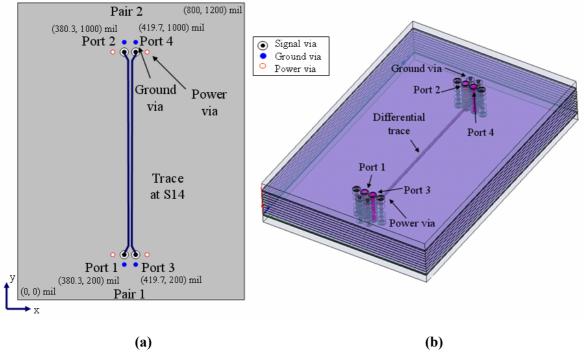

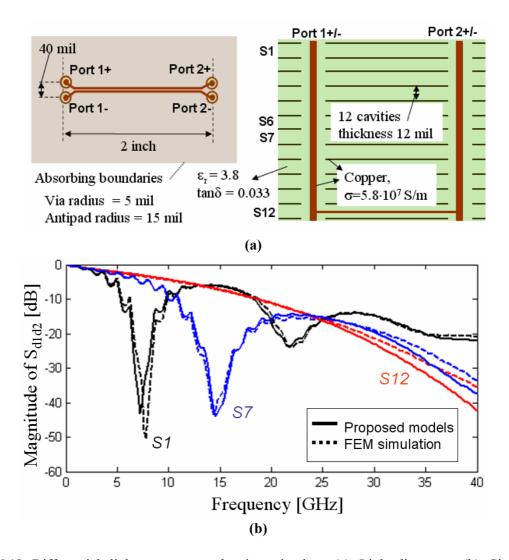

| Figure 5.19 Test structure with differential links                                        | 3 |

| Figure 5.20 Magnitude of the mixed-mode $S$ -parameters for the case in Figure 5.19 9     | 4 |

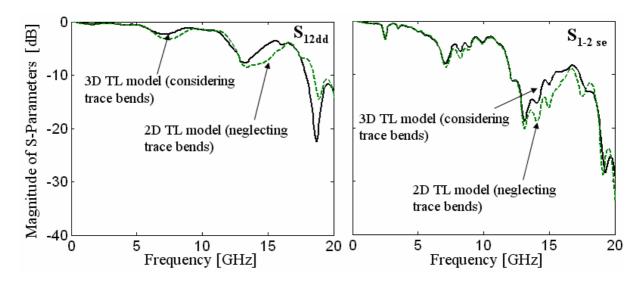

| Figure 5.21 Effect of neglecting the trace                                                |   |

| bends on differential and single-ended transmission                                       | 5 |

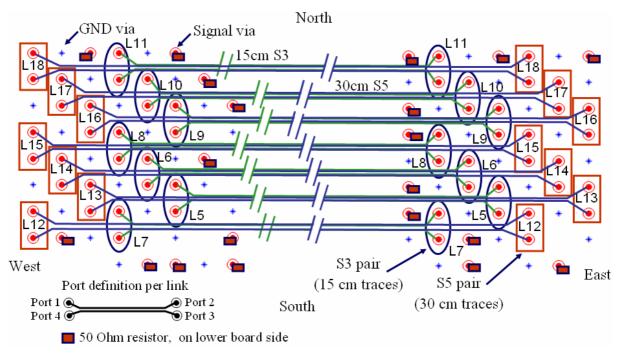

| Figure 5.22 Diagram of the differential test vehicle for model-to-hardware correlation $\dots$ | 95  |

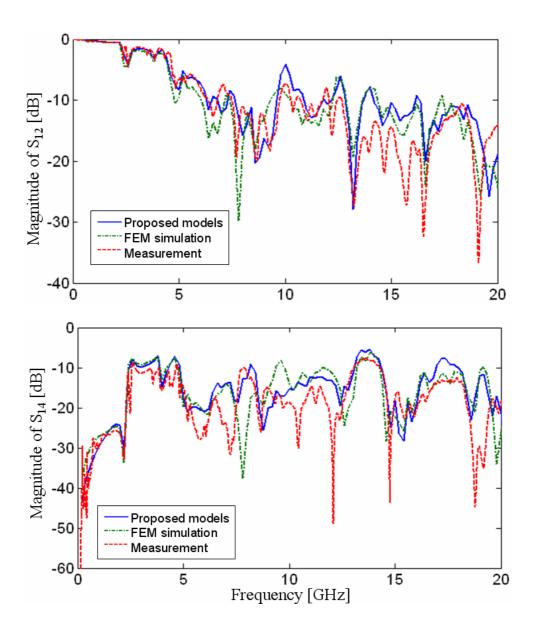

|------------------------------------------------------------------------------------------------|-----|

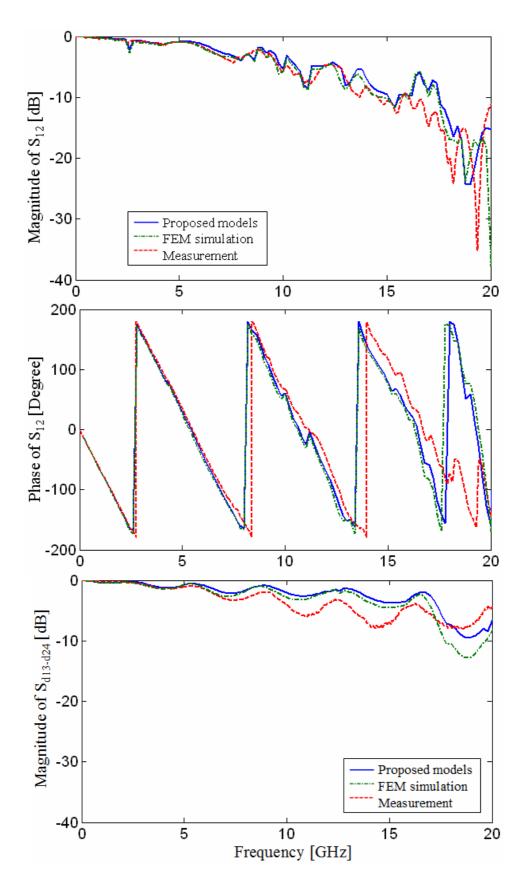

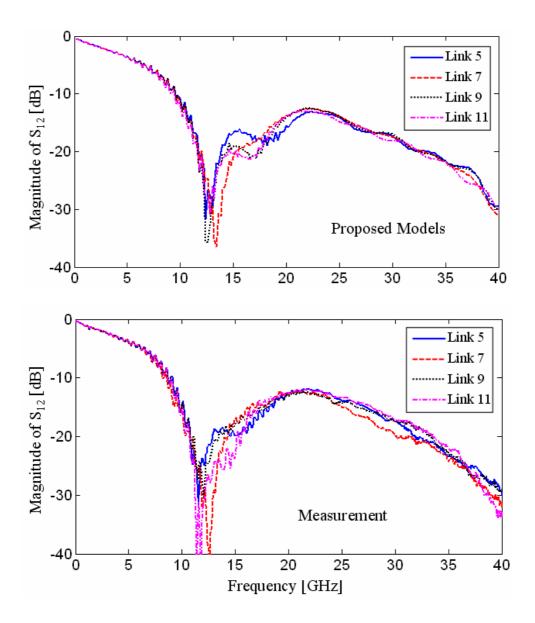

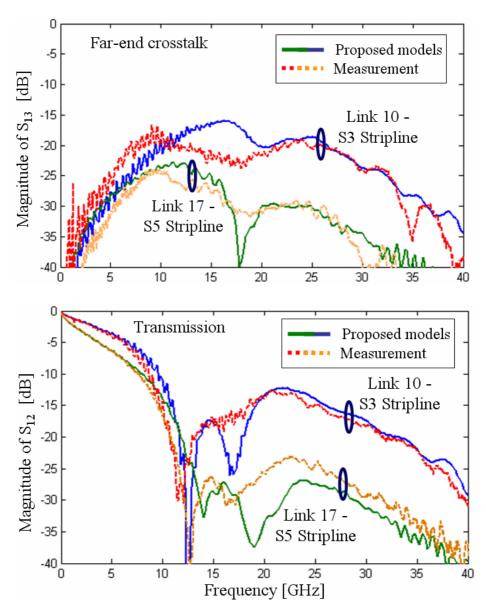

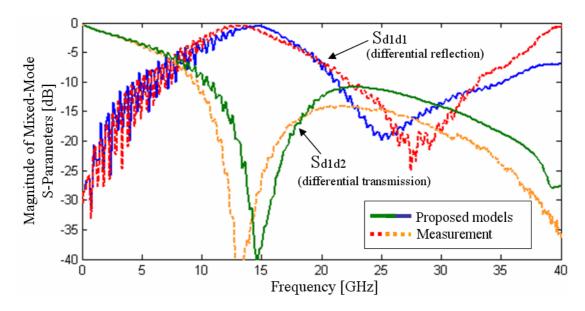

| Figure 5.23 S-parameter single-ended                                                           |     |

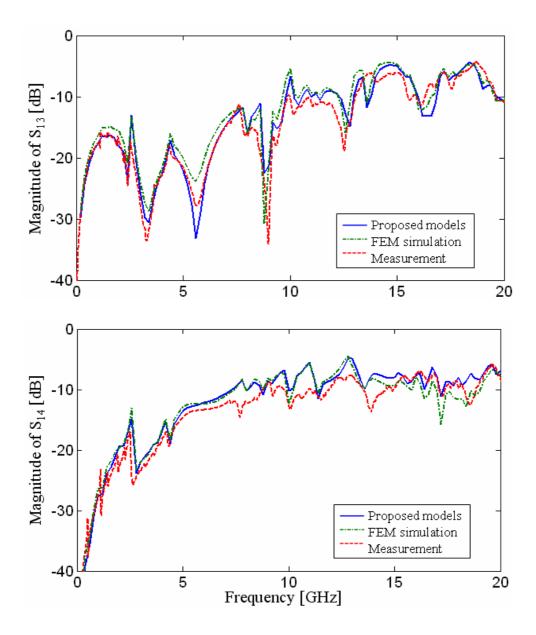

| and differential transmission for the TV-3 in Figure 5.22                                      | 96  |

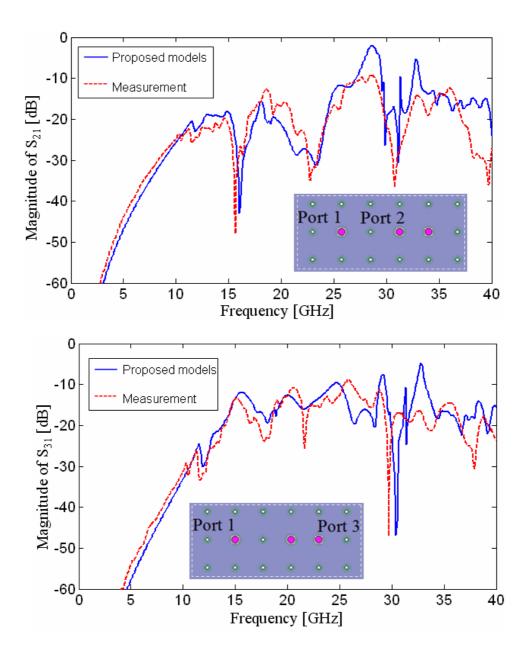

| Figure 5.24 Single-ended crosstalk parameters for the TV-3 in Figure 5.22                      | 97  |

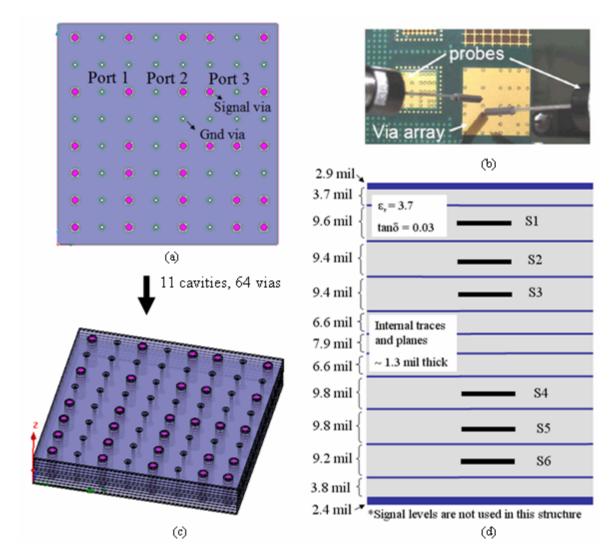

| Figure 5.25 Description of the investigated via arrays                                         | 99  |

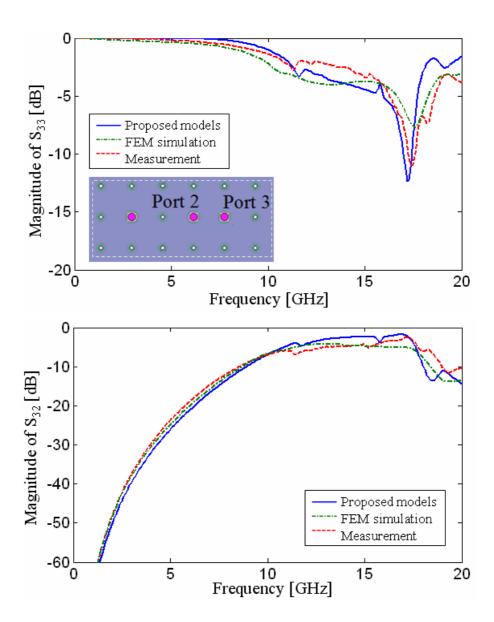

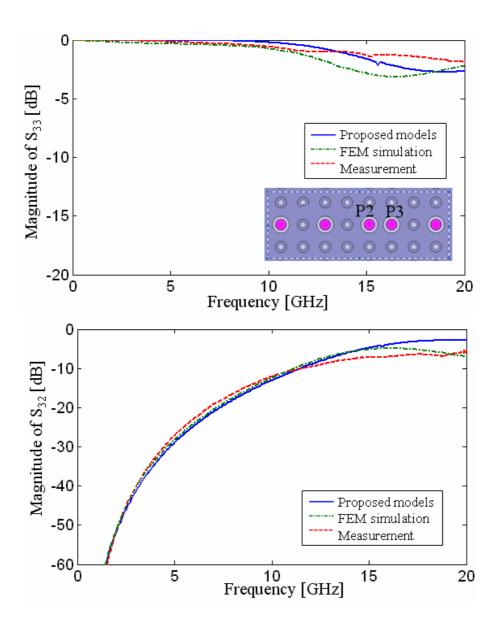

| Figure 5.26 Reflection and near-end crosstalk for the 80-mil-pitch via array                   | 100 |

| Figure 5.27 Model-to-hardware correlation                                                      |     |

| for near-end crosstalk in a 80-mil-pitch via array                                             | 101 |

| Figure 5.28 Reflection and near-end crosstalk for the 40-mil-pitch via array                   | 102 |

| Figure 5.29 Model-to-hardware                                                                  |     |

| correlation for near-end crosstalk in a 40-mil-pitch via array                                 | 103 |

| Figure 5.30 Computation time as a function of the number of vias                               | 105 |

| Figure 5.31 Computation time as a function of the number of frequencies                        | 106 |

| Figure 5.32 Computation time as a function of the number of cavities                           | 106 |

| Figure 5.33 Computation time as a                                                              |     |

| function of the number of iterations for the cavity model                                      | 107 |

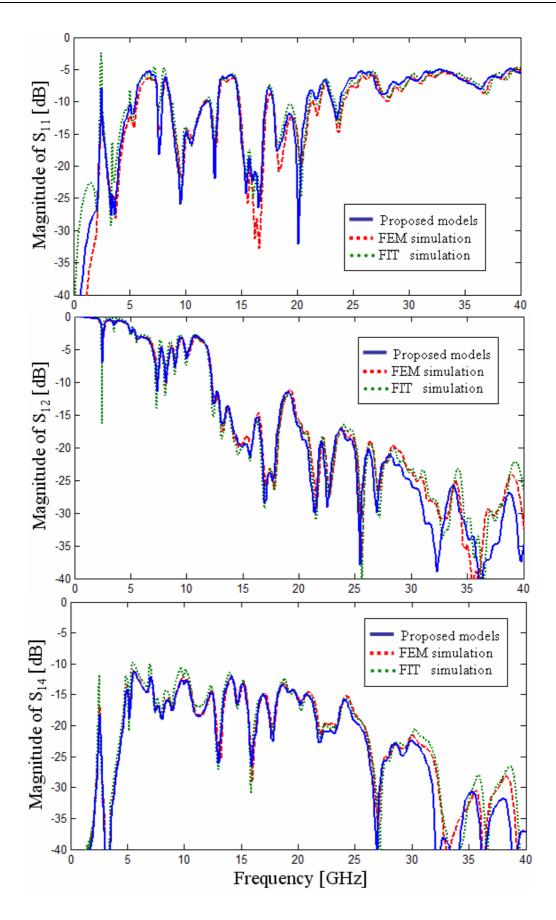

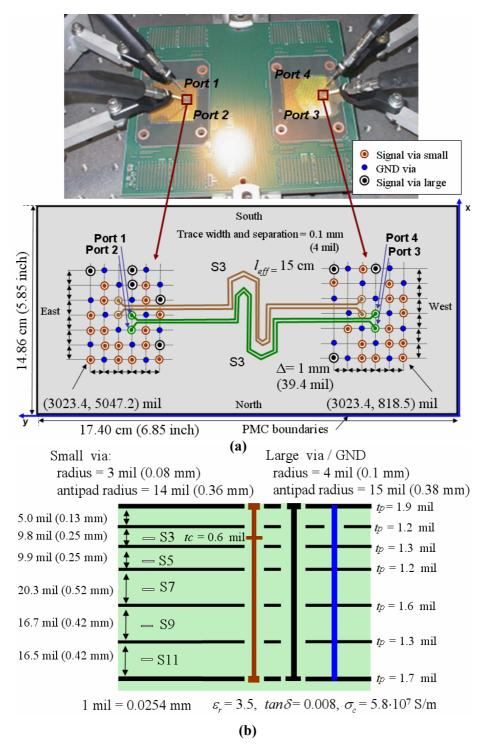

| Figure 6.1 Description of the device under test.                                               |     |

| Two BGA via arrays are connected by differential striplines                                    | 113 |

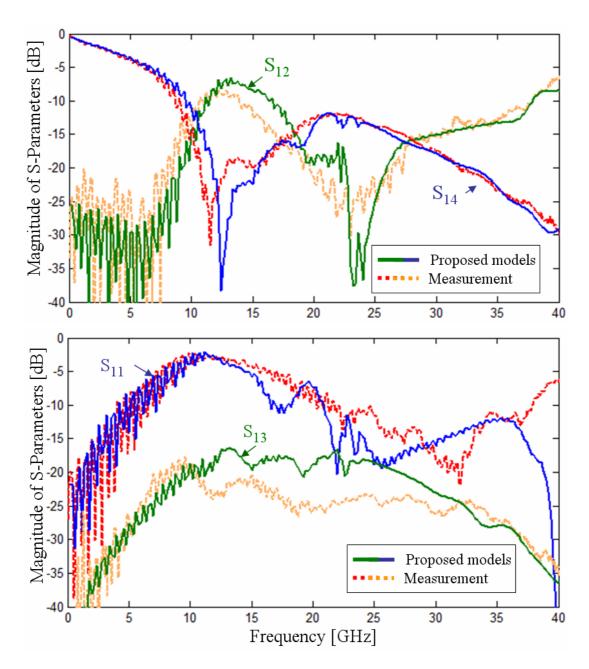

| Figure 6.2 Model-to-hardware correlation for a studied link (Figure 6.1)                       | 114 |

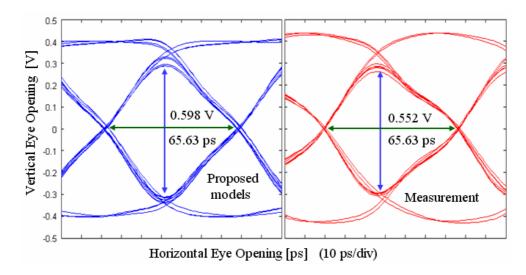

| Figure 6.3 Eye diagram for the transmission from port 1 to 4, a data rate of 15 Gb/s           | 115 |

| Figure 6.4 Diagram of the extended model for the structure described in Figure 6.1             | 116 |

| Figure 6.5 Simulated and measured                                                              |     |

| transmission for the extended link configuration in Figure 6.4                                 | 117 |

| Figure 6.6 Simulated and measured                                                              |     |

| S-parameters for the extended link configuration in Figure 6.4                                 | 118 |

| Figure 6.7 Model-to-hardware correlation for the link L5 (Figure 6.4)                          | 119 |

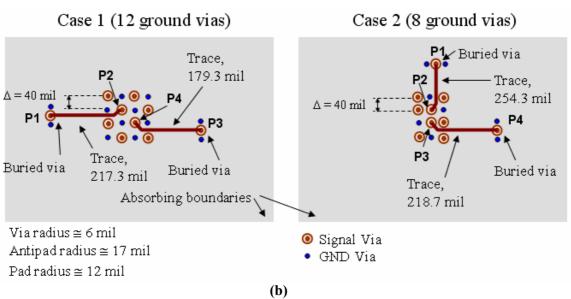

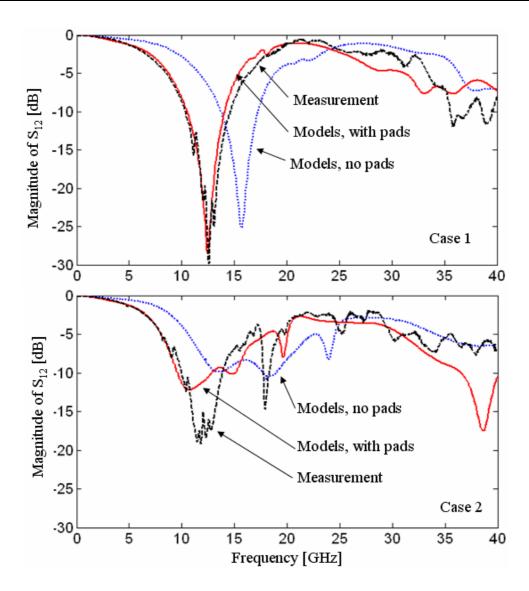

| Figure 6.8 Test structure to evaluate the stub effect                                          | 120 |

| Figure 6.9 Correlation to measurement for cases 1 and 2 in Figure 6.8                          | 121 |

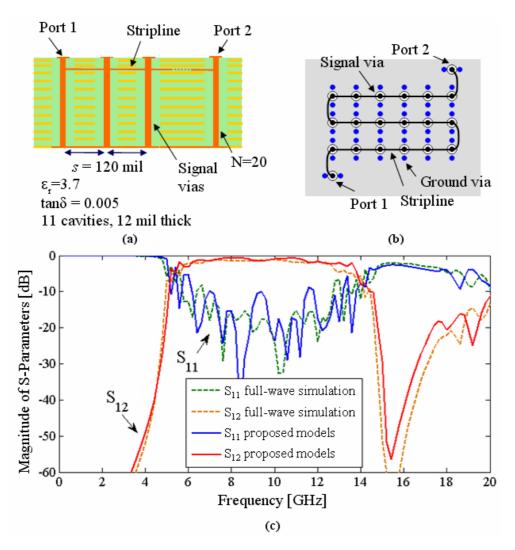

| Figure 6.10 Simulation of a periodic structure with stub vias                                  | 122 |

| Figure 6.11 Simplified description of the case of a via connected to multiple traces           | 123 |

| Figure 6.12 Model-to-hardware correlation for an array of periodic stub vias                   | 124 |

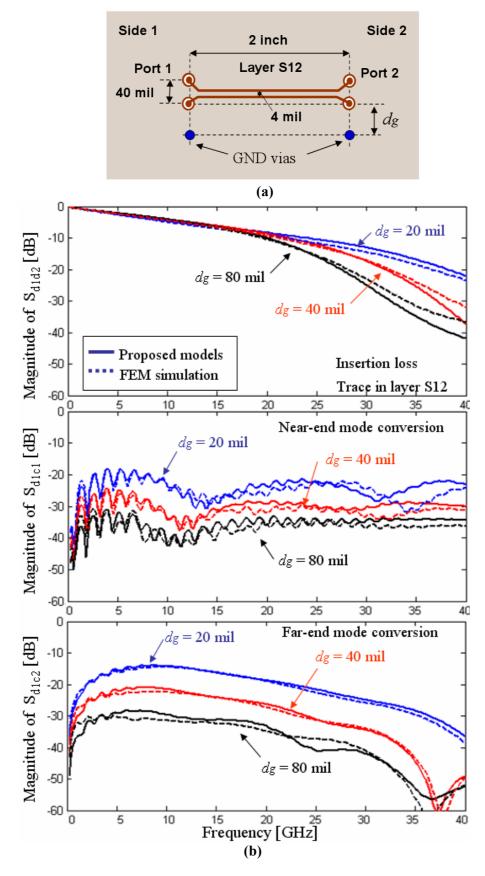

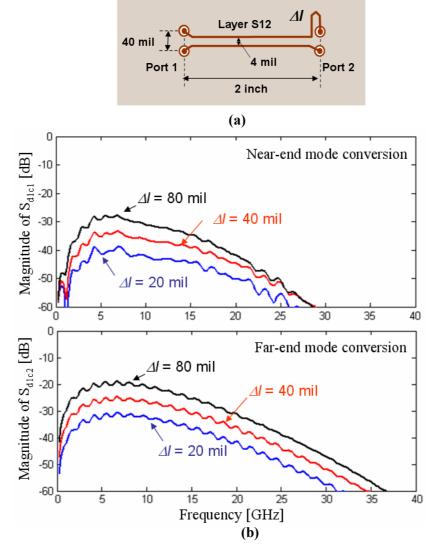

| Figure 6.13 Differential link structure under investigation                                   | . 126 |

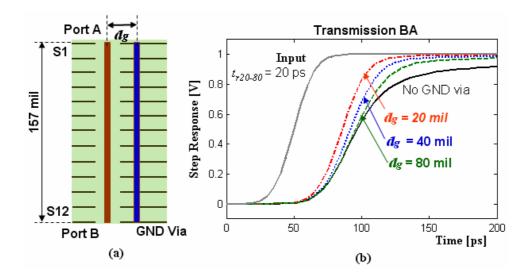

|-----------------------------------------------------------------------------------------------|-------|

| Figure 6.14 Effect of asymmetric ground vias as a function of the distance dg                 | . 127 |

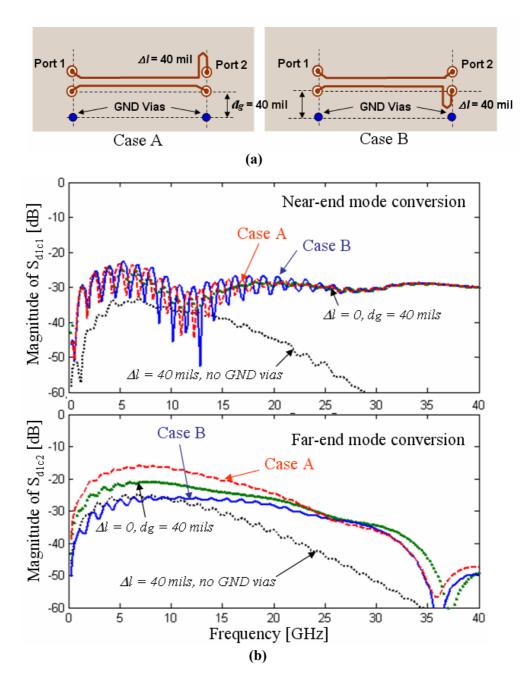

| Figure 6.15 Differential to common-mode                                                       |       |

| conversion for different asymmetric ground via configurations                                 | . 128 |

| Figure 6.16 Mode conversion in the differential link due to trace length mismatch             | . 128 |

| Figure 6.17 Mode conversion in the differential link                                          |       |

| due to the combined effect of via asymmetries and trace length mismatch                       | . 129 |

| Figure 6.18 Effect of a ground via as a                                                       |       |

| function of the separation between the signal and ground via                                  | . 131 |

| Figure 6.19 Conceptual identification of                                                      |       |

| the power and signal integrity domains in multilayer substrates                               | . 132 |

| Figure 6.20 Schematic representation of the models to include PDN elements                    | . 134 |

| Figure 6.21 Example of two differential                                                       |       |

| links routed on a multilayer substrate with mixed reference planes                            | 135   |

| Figure 6.22 Simulated differential transmission for the two links in Figure 6.21              | . 135 |

| Figure 6.23 Single-ended crosstalk between a power and a signal via, and two signal vias      | . 137 |

| Figure 6.24 Differential and common-mode interaction between a signal and a power net $\dots$ | . 138 |

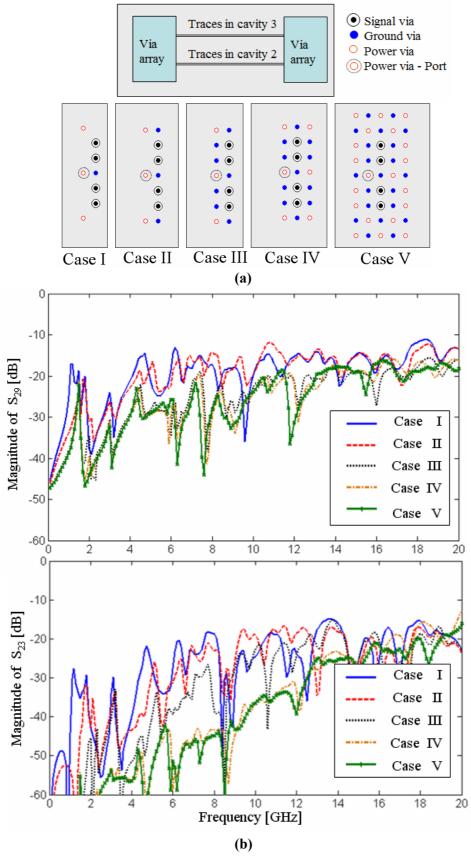

| Figure 6.25 Alternative configurations for the reference case in Figure 6.21                  | . 139 |

| Figure 6.26 Effect of decoupling capacitors                                                   |       |

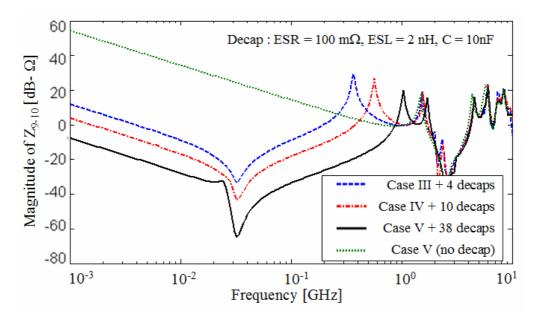

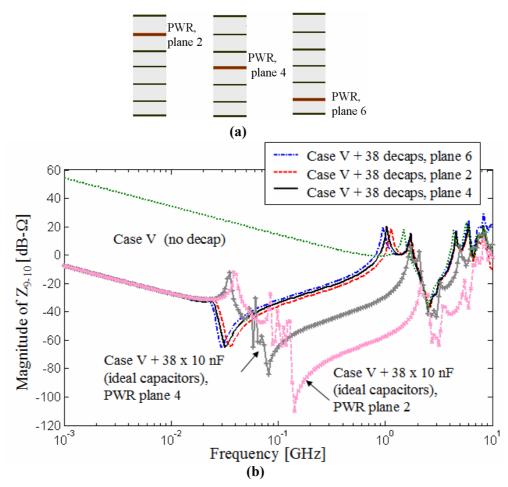

| on the transfer impedance between two power vias                                              | . 140 |

| Figure 6.27 Effect of parasitic elements associated with decoupling capacitors                | . 141 |

| Figure 6.28 Block diagram of the framework                                                    |       |

| for co-simulation of signal integrity, power integrity and radiated emissions                 | . 142 |

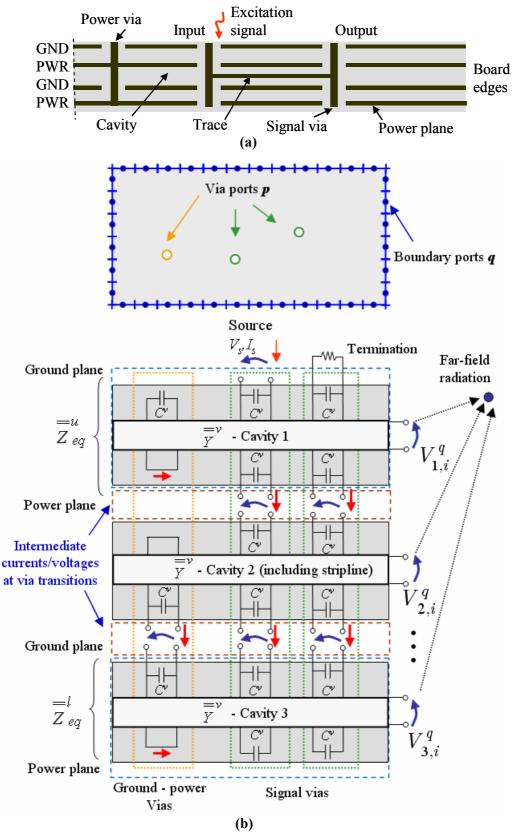

| Figure 6.29 Description of the combination process for a multilayer case                      | . 144 |

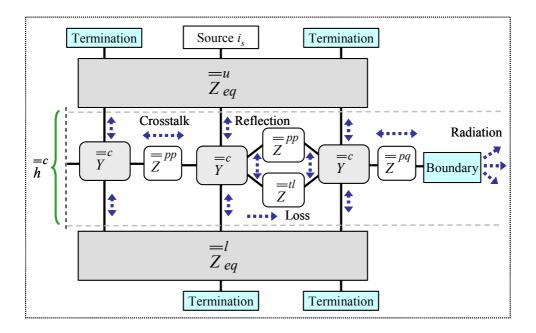

| Figure 6.30 Equivalent block diagram for                                                      |       |

| the second cavity in the example of Figure 6.29                                               | . 145 |

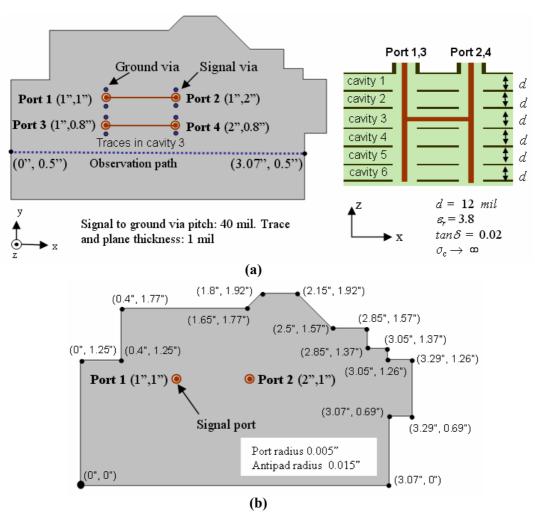

| Figure 6.31 Description of the case study                                                     | . 148 |

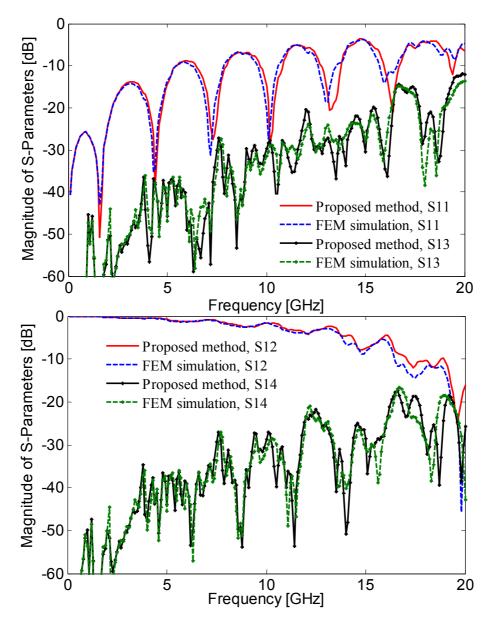

| Figure 6.32 S-parameters at the defined ports for the example in Figure 6.31                  | . 149 |

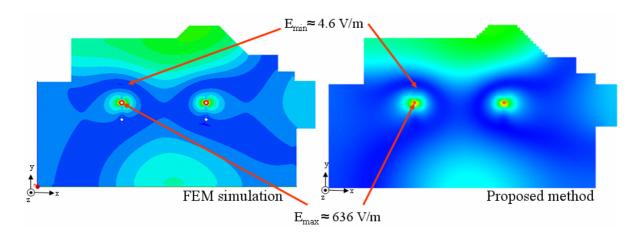

| Figure 6.33 Electric field distribution for the first cavity at 2.4 GHz                       | . 150 |

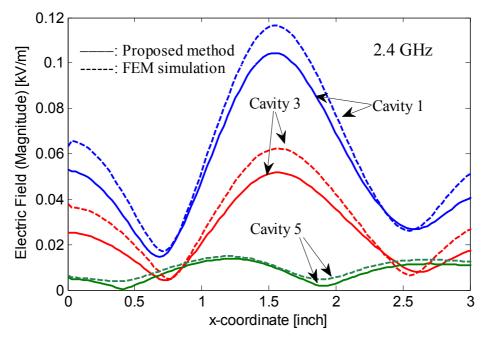

| Figure 6.34 Electric field                                                                    |       |

| distribution (complex field amplitude) along the observation path                             | 150   |

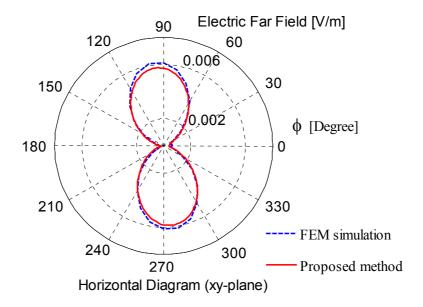

| Figure 6.35 Electric far-field radiation diagrams at 2.4 GHz and a distance of 10 meter       | . 151 |

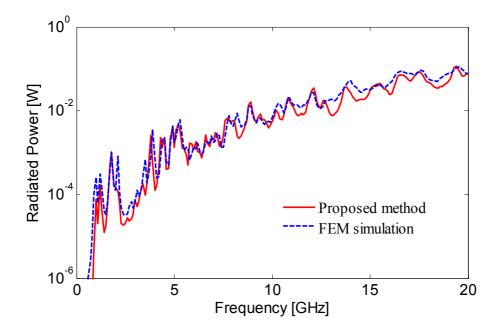

| Figure 6.36 Radiated power simulated                                               |     |

|------------------------------------------------------------------------------------|-----|

| with the proposed method and a full-wave analysis                                  | 151 |

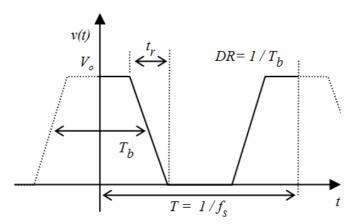

| Figure A.1 Idealized digital signal represented by an even trapezoidal pulse train | 157 |

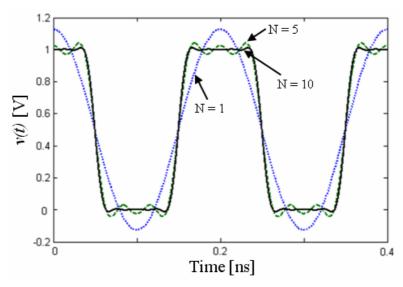

| Figure A.2 Representation of the                                                   |     |

| trapezoidal signal with a different number of harmonics                            | 158 |

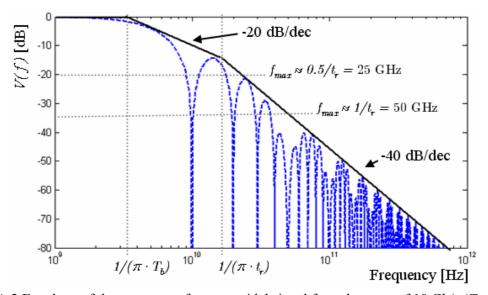

| Figure A.3 Envelope of the spectrum of a trapezoidal signal                        | 158 |

| Figure A.4 Illustration of an N-port network                                       | 160 |

| Figure A.5 Sketch for computation of the per-unit-length inductance                | 167 |

| Figure A.6 Port definition for the via and trace model                             | 170 |

| Figure A.7 Schematic representation of the segmentation method                     | 171 |

| Figure A.8 Port definition for                                                     |     |

| mixed-mode $S$ -parameters, illustrated with a four port case                      | 173 |

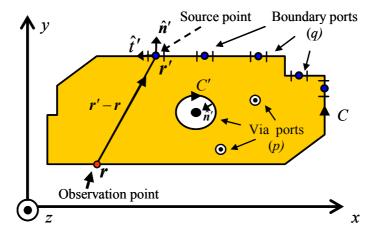

| Figure A.9 Computation domain                                                      |     |

| and variable definition for the contour integral method                            | 175 |

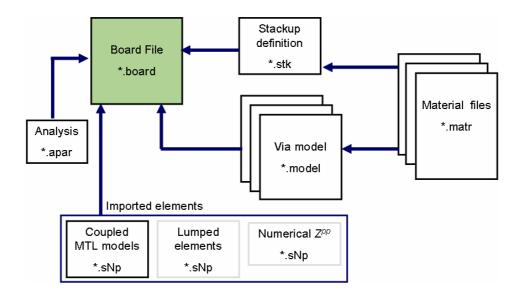

| Figure B.1 General description of the                                              |     |

| via pin field simulation tool (VPF) and its main code components                   | 178 |

| Figure B.2 Required input files for                                                |     |

| the high-level description of a multilayer substrate                               | 178 |

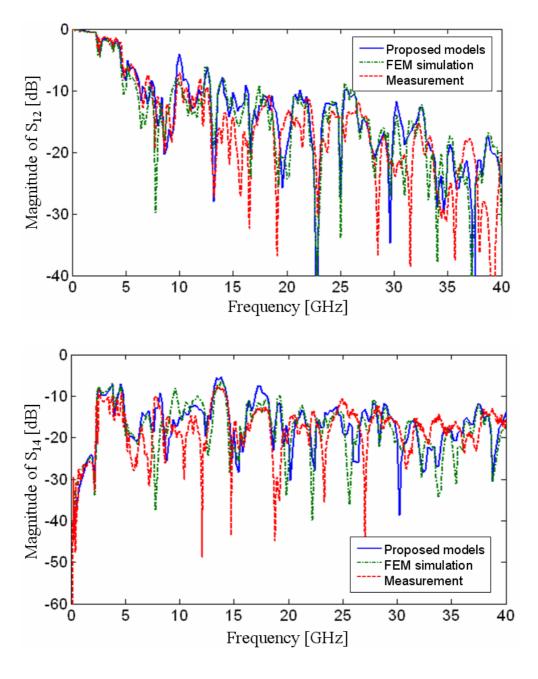

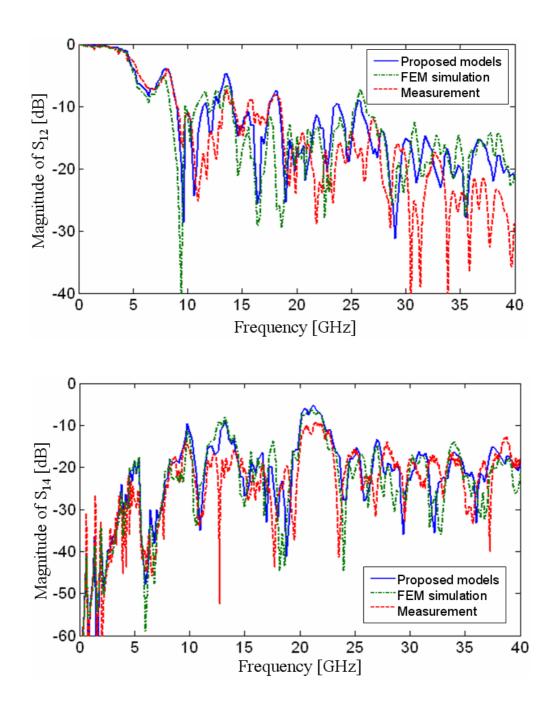

| Figure C.1 Magnitude of $S$ -parameters for the TV-1 in Figure 5.15, up to 40 GHz  | 179 |

| Figure C.2 Magnitude of $S$ -parameters for the TV-2 in Figure 5.15, up to 40 GHz  | 180 |

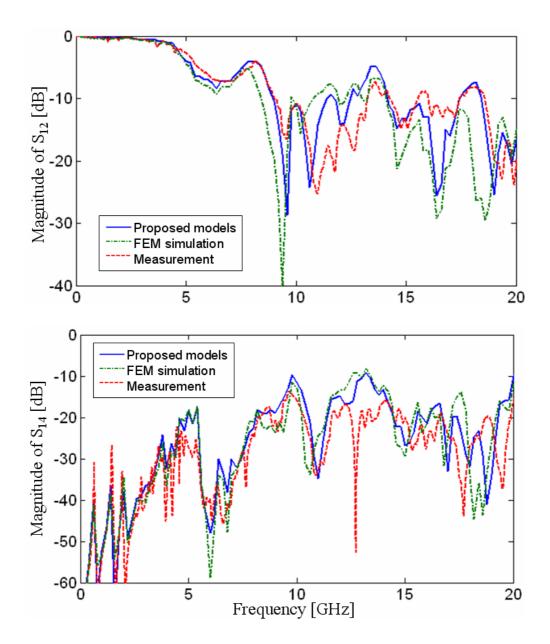

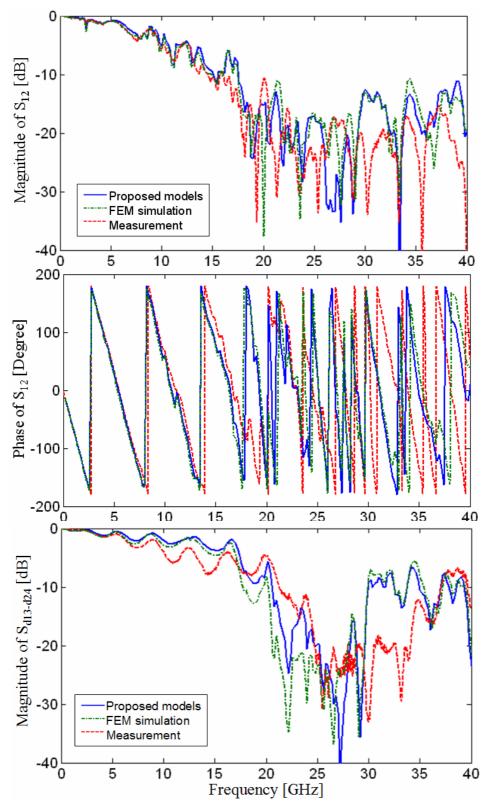

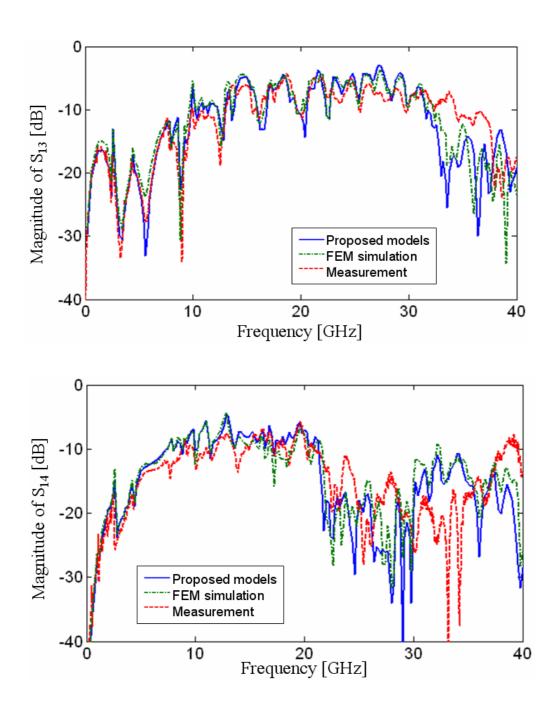

| Figure C.3 $S$ -parameter single-ended and                                         |     |

| differential transmission for the TV-3 in Figure 5.22                              | 181 |

| Figure C.4 Single-ended crosstalk parameters for the TV-3 in Figure 5.22           | 182 |

| Tables                                                                             |     |

| Table 5.1 Computation times for the example in Figure 5.1(b)                       | 75  |

| Table 5.2 Computation times                                                        |     |

| obtained by different methods for the case in Figure 5.7                           | 82  |

# List of Symbols and Acronyms

#### Notation

V Scalar

$\overline{V}$  Matrix vector

$\overline{\overline{V}}$  Matrix

T/pp Matrix entry, where indexes i and j denotes the matrix row and

column respectively, and the superscript the type of variable

$x,\ y,\ z$  Cartesian coordinates

$\rho, \varphi, z$  Cylindrical coordinates

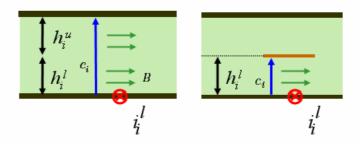

u Superscript for upper/top side of a cavity

l Superscript for lower/bottom side of a cavity

tl Superscript for transmission line modes

pp Superscript for parallel-plate modes

**R** Spatial vector

## **Symbols**

$\omega$  Angular frequency

$\alpha$  Attenuation constant

$T_b$  Bit time

C Capacitance

d Cavity thickness

$Z_0$  Characteristic impedance

G Conductance

$\sigma$  Conductivity

t<sub>n</sub> Conductor thickness (for reference planes)

$t_c$  Conductor thickness (for signal layers)

I Current

i(t) Current (time domain)

$f_c$  Cutoff/ transition frequency

$an \delta$  Dielectric tangent loss

dg Distance between a signal and a ground via (center-to-center)

$\rho_{ij}$  Distance between ports (radial waveguide method)

$h^l$  Distance from trace to bottom reference plane

$h^u$  Distance from trace to top reference plane

$\mathcal{E}$  Electric field

f Frequency

$f_s$  Fundamental frequency

$H_n^{(1)}$  Hankel function of first kind and order n

$H_n^{(2)}$  Hankel function of second kind order n

h-parameter

$\overline{\overline{E}}$  Identity matrix

j Imaginary unit

$u_{ind}$  Induced voltage

L Inductance

$L_{interc}$  Interconnect inductance (for decoupling capacitors)

a,b Lateral dimensions of rectangular plates (in x and y, respectively)

${\mathcal H}$  Magnetic field

$f_{max}$  Maximum frequency of interest

$f_{min}$  Minimum converged frequency

$T_{md}$  Modal decomposition matrix

k Modal decomposition transformation factor

$Y^{pp}$  Parallel-plate admittance

$Z^{pp}$  Parallel-plate impedance

T Period

$\mu$  Permeability (when subscripted, d: dielectric, c: conductor)

| $\mu_0$           | Permeability of free space (~ $4\pi \cdot 10^{\text{-}7} \; \text{H/m})$ |

|-------------------|--------------------------------------------------------------------------|

| $\mathcal{E}$     | Permittivity (when subscripted, $d$ stands for dielectric)               |

| $\mathcal{E}_{0}$ | Permittivity of free space (~ 8.854 $\cdot$ 10 <sup>-12</sup> F/m)       |

| β                 | Phase constant                                                           |

| $ ho_0$           | Port size (radial waveguide method)                                      |

| W                 | Port lateral size (cavity resonator model)                               |

| $\phi$            | Potential                                                                |

| γ                 | Propagation constant                                                     |

| $v_p$             | Propagation velocity                                                     |

| Q                 | Quality factor                                                           |

| $\mu_r$           | Relative permeability                                                    |

| $\mathcal{E}_r$   | Relative permittivity                                                    |

| R                 | Resistance                                                               |

| $t_r$             | Rise time                                                                |

| s                 | Separation                                                               |

| $t_s$             | Skin depth                                                               |

| S                 | S-parameter                                                              |

| t                 | Time                                                                     |

| $\Delta l$        | Trace length mismatch                                                    |

| $T_i$             | Transformation matrix for currents (modal decomposition)                 |

| $T_v$             | Transformation matrix for voltages (modal decomposition)                 |

| l                 | Transmission line/ trace length                                          |

| $Y^v$             | Via admittance (matrix)                                                  |

| $r^{ap}$          | Via-antipad radius                                                       |

| $Z^{v0}$          | Via impedance                                                            |

| $r^p$             | Via-pad radius                                                           |

| $r^v$             | Via radius                                                               |

| $Y^c$             | Via-to-plane admittance                                                  |

| $C^v$             | Via-to-plane capacitance                                                 |

| $C^{vb}$          | Via-to-plane capacitance of a buried via                                 |

| $C^c$             | Via-to-plane coaxial capacitance                                         |

$C^f$  Via-to-plane fringing capacitance

$Z^c$  Via-to-plane impedance

$C^b$  Via-to-plane lateral capacitance

V Voltage

$\eta$  Wave impedance

k Wave number

$\lambda$  Wavelength

Y Y-parameter

Z Z-parameter

#### Acronyms

2D Two Dimensional

3D Three Dimensional

ABC Absorbing Boundary Condition

ABCD Microwave Network Chain Parameters

AC Alternating Current

BGA Ball Grid Array

C Capacitance

CIM Contour Integral Method

CISPR International Special Committee on Radio Interference (in French)

CRM Cavity Resonator Model

CM Common-Mode

CRM-DS Cavity Model – Double Summation

CRM-SS Cavity Model – Single Summation

CRM-SSi Cavity Model – Single Summation (improved)

CPU Central Processing Unit

DC Direct Current

DDR Dual Data Rate (for Random Access Memories)

Decap Decoupling Capacitor

DM Differential Mode

DR Data Rate

DVI Digital Visual Interface

EM Electromagnetic

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

ESL Equivalent Series Inductance

ESR Equivalent Series Resistance

FCC Federal Communications Commission

FDTD Finite Difference Time Domain Method

FEM Finite Element Method

FFT Fast Fourier Transform

FIT Finite Integration Method

FSV Feature Selective Validation

FWHM Full Width Half Maximum

GND Ground

GS/SG Ground Signal / Signal Ground

h – Microwave Network Hybrid Parameters

HTCC High Temperature Co-fired Ceramic

HFSS High Frequency Structure Simulator (FEM Solver)

IBM International Business Machines Corp.

IC Integrated Circuit (or chip)

IFFT Inverse Fast Fourier Transform

ITRS International Technology Roadmap for Semiconductors

LAN Local Area Network

LGA Land Grid Array

LTCC Low Temperature Co-fired Ceramic

MAN Metropolitan Area Network

MCM Multi-chip Module

M-FDM Multilayered Finite Difference Method

MoM Method of Moments

MTL Multiconductor Transmission Line

PC Personal Computer

PCB Printed Circuit Board

PCIe Peripheral Component Interconnect Express

PDN Power Distribution Network

PEC Perfect Electric Conductor

PEEC Partial Element Equivalent Circuit Method

PI Power Integrity

PLL Phase-Locked Loop

PMC Perfect Magnetic Conductor

PML Perfectly Matched Layer

PWR Power

RAM Random Access Memory

RE Radiated Emissions

RLC Resistance-Inductance-Capacitance

RPL Recessed Probe Launch

RW Radial Waveguide

RW-IT Radial Waveguide – Image Theory

Rx Receiver

S- Microwave Network Scattering Parameters

S[X] Signal Level [X]

SA-SCSI Serial Attachment – Small Computer System Interface

SATA Serial Attachment (Interface)

SBU Sequential Build-Up

SerDes Serializer-Deserializer

SI Signal Integrity

SiP System in Package

SMT Surface Mount Technology

SoC System on Chip

SOLT Short Open Load Thru (Calibration Procedure)

SoP System on Package

SPICE Simulation Program with Integrated Circuit Emphasis

SSN Simultaneous Switching Noise

TE Transfer Electric

TEM Transfer Electric Magnetic

TET Institut für Theoretische Elektrotechnik, TUHH

TL Transmission Line

TLM Transmission Line Matrix Method

TM Transfer Magnetic

TMM Transmission Matrix Method

TSV Thru Silicon Vias

TUHH Technische Universität Hamburg-Harburg

TV Test Vehicle

Tx Transmitter

USB Universal Serial Bus

VNA Vector Network Analyzer

VIA Vertical Interconnect Access

VPF Via Pin Field (Simulation Tool)

VRM Voltage Regulator Module

WAN Wide Area Network

Y- Microwave Network Admittance Parameters

Z- Microwave Network Impedance Parameters

## 1. Introduction

#### 1.1. Motivation and Context of this Work

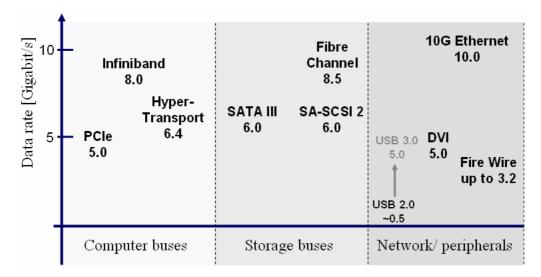

Modern high-speed electronic systems often require thousands of off-chip interconnects to interface heterogeneous components such as processing units, memory, storage devices, and network interfaces. The trends towards miniaturization and higher data rates that have driven the electronic industry in the past few decades demand high-density interconnects operating in the multi-GHz range. For instance, multi-chip-modules (MCM) and high-performance printed circuit boards (PCBs) are commonly found in commercial products [1]-[2]. Moreover, several high-speed specifications for wired links —such as PCIe, SATA, DDR-3, or 10G Ethernet— have become industry standards, many of them targeting data rates in excess of 10 Gigabits per second (Gb/s) [3]-[4] (Figure 1.1).

Off-chip interconnects constitute the bottleneck for the maximal achievable data rate, since they introduce frequency dependent degradation and distortion on signal paths [5]. The efficient modeling and simulation of off-chip interconnects have become essential to assist the design process and to look for the best trade-off between cost and performance. This is a challenging task because of the large number of elements and the complicated electromagnetic field effects that must be considered to model a realistic scenario. General-purpose numerical methods can be used to describe interconnects accurately, but often become inefficient to handle complex configurations and to perform trade-off and optimization studies. In contrast, simplified quasi-static models usually fail to describe the high-frequency behavior and the multiple coupling mechanisms of interconnect systems. According to the international technology roadmap of semiconductors ITRS 2009 [6], the development of accurate and efficient compact models for high-frequency circuits and systems is a challenge of prime importance in order to enable the concurrent design and optimization of integrated circuits (ICs), passives, and substrates.

In the category of off-chip interconnects, multilayer substrates, often used in packages and PCBs, constitute an important resource for integration of digital, analog, and passive components. Nowadays, this type of substrate can be found in almost any

2 Introduction

**Figure 1.1** Some high-speed standards for digital systems and their maximal data rates (in 2009).

electronic system, from hand-held devices to mainframe servers, communication, and space applications [7].

This work is a contribution to the topic of efficient modeling and simulation of multilayer substrates. Semi-analytical models for the electrical behavior of vias and traces in parallel-plane environments have been proposed and validated against other numerical techniques and measurements. The models have been incorporated into an automated simulation method that has been successfully applied to signal integrity, power integrity, and electromagnetic interference analyses in a comprehensive and very efficient manner. At the present time, it is possible to handle relatively complex structures with hundreds of signal and power/ground vias, tens of mixed reference planes, several coupled traces, and lumped elements such as decoupling capacitors. The utilization of these models allows a reduction of the computation time by a factor between two and three orders of magnitude when compared to general-purpose numerical methods for electromagnetic field simulation.

## 1.2. Organization of the Work

The bulk of this thesis is organized into six chapters, whose contents are detailed as follows.

Chapter 2 presents a very brief introduction to multilayer substrate technologies. The main concerns in relation to signal integrity, power integrity, and electromagnetic compatibility are reviewed and references for further reading are provided. The state of the art methods for modeling and simulation of multilayer substrates are overviewed in the last subsection.

Introduction 3

Chapter 3 reviews the physical effects associated with vias, which are fundamental for understanding the field coupling mechanisms in multilayer substrates. The addressed topics cover the excitation of parallel-plate modes, effects of return vias, and crosstalk. The extraction of via transmission line parameters, the impact of via geometry, and the stub effect are discussed as well.

Chapter 4 explains the modeling approach, the proposed models, and their mathematical formulation in terms of microwave network parameters. The via model and different alternatives to compute its building blocks are addressed in this chapter. Analytical techniques to compute the parallel-plate impedance are reviewed, compared, and a hybrid method is proposed. Alternatives to compute the via-to-plane capacitance and the extension of the via model to consider traces by applying a modal decomposition technique are also covered. Finally, the approach used for partial result concatenation and the general simulation framework for multilayer substrates are introduced.

Chapter 5 deals with the validation of the models. The presented examples cover the simulation of multilayer via configurations, single-ended and differential links, and via arrays. The described structures include signal, power, and ground vias with mixed-reference planes, buried and blind via configurations. The results are compared against general-purpose full-wave solvers and hardware measurements. The numerical efficiency of the models is also discussed and, in the last section, model limitations and perspectives for further developments are provided.

Chapter 6 presents the application of the models to signal integrity, power integrity, and electromagnetic interference problems. The case studies cover the simulation of differential links across ball grid via arrays (BGA), the via stub effect, and mode conversion in differential links. The co-analysis of power and signal integrity, and the impact of power/ground via design and surface decoupling capacitors are discussed next. In the last section, the extension of the method to the combined simulation of signal propagation, ground bounce, and radiated emissions is explained.

Chapter 7 gathers the main results of this work. The contributions of this thesis are briefly reviewed and pros and cons of the modeling approach are discussed. Recommendations for further work are also provided.

4 Introduction

#### 1.3. Conference and Journal Contributions

As part of this work several conference [8]-[16] and journal contributions [17]-[19] have been made in the field of model development, efficient simulation, and analysis of multilayer substrates. These publications constitute a fundamental part of this thesis. During the development of this project the author has also contributed to a number of publications in related topics [3],[20]-[27].

Much of this work has been done in cooperation with industry and other university research groups. The main external collaborators were the High-Speed I/O Subsystems and Packaging Group at IBM T. J. Watson Research Center, who also provided the test hardware and most of the measurements presented in Chapters 5 and 6, and the Electromagnetic Compatibility Laboratory at the Missouri University of Science and Technology.

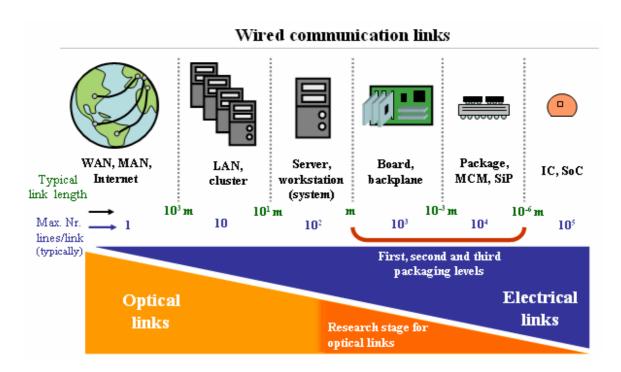

# 2. Multilayer Substrates in High-Speed Electronic Systems

The main task of interconnects is to allow the flow of information between diverse components of an electronic system. They also provide the mechanical support and the interface for heterogeneous technologies [7],[29]. Interconnects are necessary at all levels of hierarchy, from integrated circuits up to overseas communication links. Optical technologies are ubiquitous in very long distance applications; however, short interconnects are still the domain of wired links using metallic conductors, typically Copper (see Figure 2.1). Although the realization of short optical links has been demonstrated, e.g. in [30], important cost and fabrication obstacles have to be overcome before their widespread adoption [31]. For this reason, the improvement of wired technologies through the miniaturization of systems and the development of global and more efficient modeling strategies are currently active research fields [32]-[33].

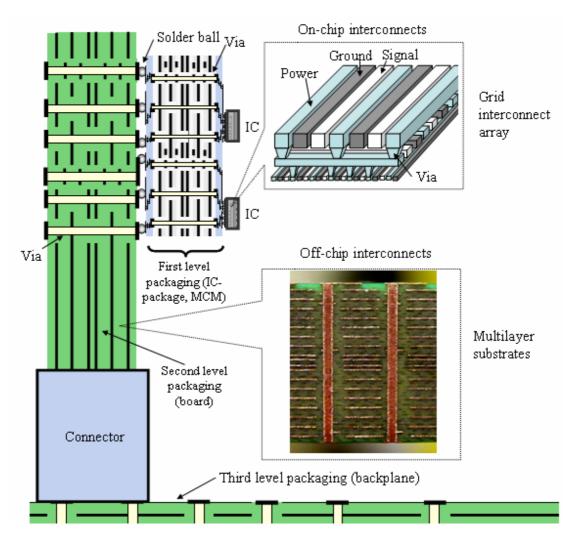

As depicted in Figure 2.2 for systems using "short" electrical links, interconnects can be classified into two main categories:

- On-chip, formed by the metallization layers of IC technologies and pads that provide the interface to the next packaging level. For dense digital circuits they are typically organized as grid arrays [34].

- Off-chip, defined by the first, second, and third packaging levels. They comprise multilayer substrates at package and board levels, as well as other elements such as bond wires, solder balls, pins, connectors, sockets, cables, etc. [29]. This second category is the one of interest for this work and it will be briefly discussed in the next section.

## 2.1. Multilayer Substrate Technologies

Multilayer substrates are commonly formed by stacked power/ground levels and signal layers that are linked to each other by vertical interconnects, called *vias* (Figure 2.2).

Laminated substrates are fabricated by alternating *core* and *prepreg* layers. The core is a cured dielectric layer bounded by two metallic plates, whereas the prepreg is an uncured dielectric material often consisting of woven glass sheets impregnated with

**Figure 2.1** Utilization of optical and electrical links for high-speed communications and digital systems. Adapted from [31].

epoxy resin. The prepreg is used to bond multiple stacked cores in a single step by applying heat and pressure. The final arrangement of cores and prepreg layers is known as *stackup* [29]. The circuitry is formed by etching conducting patterns on the metal plates prior to lamination and interconnecting the different levels by means of vias [35]. Vias are usually created by drilling holes spanning the full stackup and subsequently plating a metal (typically Copper) on the walls.

Sequential built-up processes (SBU, also called build-up) are used for high performance boards that require higher densities or drastic geometry size changes. In SBU each layer is processed separately. The vias, called *microvias*, can be formed by photo-processes, etching, or laser drilling [35]. SBU allows the fabrication of smaller interconnect elements in comparison to laminated processes, such as buried microvias.

A multilayer substrate may contain both laminated and SBU regions, as depicted in Figure 2.3. Bond wires or solder balls are used to interface the package with ICs, whereas solder balls or pins may serve to reach the next package level. Metallic pad regions are used to interconnect vias with other elements such as traces, decoupling capacitors, or solder balls. Clearance holes, known as antipads, are etched into the planes in order to isolate vias when connectivity to the plane is not desired.

First level packages can be made with organic materials (e.g. epoxy resins, polymides), ceramics (e.g. HTCC, LTCC), or other plastic and flex-film compounds [7].

**Figure 2.2** Illustration of interconnect levels in high-speed electronic systems. On-chip interconnects mainly consist of metallization layers of IC technologies, which are typically arranged as grid meshes. Off-chip interconnects cover the first (package and MCM), second (board), and third (motherboard/backplane) levels. Multilayer substrates are used to support the off-chip signal and power networks.

Organic packages offer a low-cost solution, whereas ceramic packages provide better mechanical performance and higher wiring and pin densities [31]. With SBU processes, microvias can have diameters below 50 microns (µm) and center-to-center separations (pitch) starting from 100 microns. MCM modules and chip stacking are other available package technologies that allow the integration of several ICs, including processors and cache memory. Silicon carriers with through silicon vias (TSV) have been reported in the literature as an alternative which allows stacking of multiple dies (3D integration or System-in-Package) [32],[36]. TSV diameters are typically in the micron (µm) range, from 0.1 up to several tens of microns [36].

Similarly to low-cost packages, conventional PCBs are fabricated by lamination processes. High density boards may have over 25 metallic layers and can be made with a wide variety of dielectric materials and copper-based foils. Reinforcement cloths can also be incorporated in the dielectric regions in order to provide dimensional stability

Figure 2.3 Diagram of a multilayer substrate combining a laminated core with sequential built-up layers.

**Figure 2.4** Multilayer printed circuit board (PCB) cross section. All reference planes are connected to ground vias and two signal levels can be identified on the cut. *Photo courtesy of Y. H. Kwark, IBM T. J. Watson Research Center, NY, USA.*

during reflow and rework processes [37]. Typical separations between metallic levels can be as low as 2.5 mil (1 mil  $\approx 25.4 \ \mu m$ ) and up to 30 mil. Through-via diameters for high-performance applications range between 8 and 16 mil ( $\sim 0.2$  - 0.5 mm), with antipad diameters from 15 to 40 mil and a via pitch of around 40 mil ( $\sim 1 mm$ ). With SBU higher densities can be achieved. Microvias can have diameters below 2 mil [38]. Figure 2.4 shows a photograph of a multilayer PCB cross-section. Available processes and technologies for packages and PCBs are widely discussed in several books, for instance in [7],[37]-[38].

The present work is focused on the efficient modeling of the portion of the substrate enclosed between solid reference planes, which are affected by the excitation of parallel-plate modes [19]. The fact that at high frequencies the vias and the reference planes become tightly coupled has significant signal integrity (SI), power integrity (PI) and electromagnetic compatibility (EMC) implications. The next sections briefly review the main concerns from each one of these three perspectives in relation to the reliable design of off-chip interconnect systems.

#### 2.2. Signal Integrity

Signal integrity is concerned with the reliable transmission of information across the different interconnect hierarchy levels [39]-[40]. Passive wired interconnects are band limited, typically showing a low-pass characteristic. It is therefore important to ensure that the channel is able to transmit necessary frequency components of the signals without excessive degradation. The bandwidth of digital signals depends on the rise time  $t_r$  and it can be estimated from the analysis of idealized waveforms [39] (See Appendix A.1). For a given data rate (DR), the bit time is  $T_b = 1/DR$  and the fundamental frequency is  $f_s = 1/T = 1/(2T_b)$ . A typical  $t_r$  value is about  $0.1 \cdot T$  and the maximum frequency content of the signal can be approximated as  $f_{max} \approx 1/t_r$ . For instance, for a 10 Gb/s signal, the fundamental frequency is 5 GHz,  $t_r \approx 20$  ps, and  $f_{max} \approx 50$  GHz. A less stringent criterion which uses  $0.5/t_r$  to include about 90 % of the frequency content yields  $f_{max} \approx 25$  GHz [41]. These quick estimates allow judging the interconnect performance and the required bandwidth of the models used to describe the channel.

A signal transmitted over off-chip interconnects can suffer degradation (in magnitude and phase) due to [5],[42]:

- Frequency dependent dielectric and conductor loss.

- Reflections at discontinuities such as vias and plane perforations.

- Noise sources such as crosstalk from other signal nets as well as switching noise coupled in through the power distribution network.

**Figure 2.5** Simplified diagram of a high-speed serial link (SerDes). Equalizers at transmitter (Tx) and receiver (Rx) sides are used to compensate the channel degradation at higher frequencies. A more detailed treatment of the topic can be found in [42]-[44]. Heuristically, the task of the equalizers is to compensate the low-frequency response of the channel by emphasizing the high-frequency components of the signals. PLL stands for phase-locked loop and it is used to provide an stable clock reference.

These effects can be mitigated by proper design of the passive channel, which includes the selection of the substrate, stackup, via types and position, number and position of ground and power vias, routing of signal paths, type of signaling, utilization of decoupling capacitors, etc..

For links working at multi-gigabit data rates, active digital circuits are frequently required to further compensate the channel degradation (Figure 2.5). Equalization techniques are used to "flatten" the frequency response of the channel by counterbalancing its low-pass characteristic by means of "high-pass" analog and digital filter operations [42]-[44]. Nevertheless, additional circuits are expensive in terms of area and power consumption, and therefore the optimization of the interconnects aiming at a reduction of the necessary on-chip circuitry is highly desirable.

## 2.3. Power Integrity

The function of the power distribution network (PDN) is to provide a clean and reliable supply voltage to all system components and a good return path for signals. The most important components of a PDN are the main DC supply source, voltage regulator modules (VRM or DC-DC converters), decoupling capacitors, and the associated interconnects [45]. At package and board levels, the PDN interconnects are mostly formed by the reference planes, and the ground and power vias used to link them (Figure 2.6). Although power meshes can also be used at package level [46], stacked solid planes are usually preferred since they can provide a lower PDN impedance and

the inter-plate capacitance may help to reduce crosstalk and electromagnetic interference.

The voltage and current variations on the PDN induce power noise through the parasitics associated with on- and off-chip interconnects, which may affect the amplitude (under/over shot) and delay (jitter) of information signals. It is therefore desirable to control the PDN impedance to get very small impedance values. In fact, modern integrated circuit technologies demand target impedances in the milli- $\Omega$  range [45].

The simultaneous switching noise (SSN) [47], also called  $\Delta i$  noise, is perhaps the most important mechanism for power noise generation. This phenomenon takes place when many digital circuits change states simultaneously and the associated peak in the current demand induces a transient voltage drop on the PDN. This voltage is, in a first order approximation, proportional to the equivalent inductance of the interconnects  $L_{eq}$

$$v_{ind}(t) = L_{eq} \cdot \frac{di(t)}{dt} \tag{2.1}$$

Unlike other noise sources, the SSN is deterministic since it can be related to the period of the signal transitions [39]. This type of noise can be either generated on chip, due to IC core circuits and drivers switching, or off chip, due to signals traveling on signal nets at package and board levels. The power noise can be mitigated by [39]:

• Limiting the rise time of the signals in order to reduce the di/dt magnitude (which is in conflict with signal integrity interests of high data rates and signal detection).

**Figure 2.6** Diagram of a power distribution network main components at board and package levels. Voltage regulator modules and decoupling capacitors (C) are used to provide a reliable power supply.

- Reducing the interconnect inductance. This is achieved for off-chip PDNs by using solid power and reference planes located in close proximity and by optimizing the placing of PDN components.

- Bypassing the PDN impedance with decoupling capacitors.

While the VRM provides a large charge reservoir for the circuits, it can not always meet the demands quickly enough due to the parasitic inductance of the PDN. In this time domain picture, decoupling capacitors serve as additional charge sources that can be placed closer to the chips and help to maintain the voltage level at the moment when several gates switch and the current demand drastically increases [48]. In the frequency domain, the task of these capacitors can be seen as the reduction of the equivalent PDN impedance by providing a low impedance path between power and ground nets (bypassing). However, non-ideal decoupling capacitors possess parasitic inductance and resistance, which limit their practical effectiveness [49]. Larger capacitors can provide more charge but have larger parasitics -both internally and due to their associated interconnects—that make them effective only at lower frequencies. Smaller capacitors can be placed closer to the problematic nets and are more effective at higher frequencies. The decoupling scheme in modern electronic systems requires many capacitors placed at all levels of the interconnect hierarchy, from electrolytic and surface capacitors at board and package levels up to embedded package and on-chip capacitors [45].

### 2.4. Electromagnetic Compatibility

Electromagnetic compatibility addresses the design of electronic systems that do not cause electromagnetic interference (EMI) to other devices, and are not susceptible to EMI coming from other systems [50]. The EMI emissions can be *conducted* and pass to the common AC power net, or they can be *radiated* directly from the device. The conducted emissions can be transformed to radiated emissions at the power nets [51].

Devices and interconnects placed on multilayer substrates, such as microstrip lines or plane discontinuities, can become a source of EMI. Radiated emissions can also be originated at the board edges, in particular at higher frequencies. Other sources of interference are ICs and cables attached to boards. The mitigation of emissions can be achieved either by suppression of the EMI source, elimination of the coupling paths, or reduction of the susceptibility of the devices by increasing noise margins [50].

Emissions are regulated by standards set by governmental agencies, such as the Federal Communications Commission (FCC) in the United States and the International Special Committee on Radio Interference (CISPR) in the European Union [50]-[51]. These standards attempt to control EMI pollution, but do not guarantee the

functionality of a system; therefore, manufacturers may impose additional requirements, particularly for devices working in the GHz range.

SI, PI, and EMC are three closely related, yet different aspects of the electromagnetic nature of digital interconnects. For instance, common-mode currents of signal nets and SSN are important sources of radiated emissions [50]. A good design methodology should be able to address the interdependences between these different perspectives.

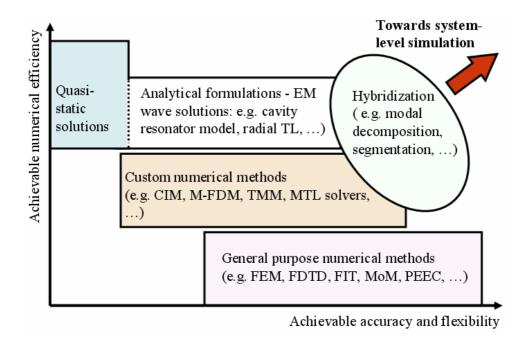

## 2.5. Overview of Techniques for High-Frequency Modeling of Multilayer Substrates

Analytical approximations, simplified static and quasi-static models for interconnect elements—like some formulae provided, for instance, in [41],[52]-[53]— have proven to be useful in developing understanding and performing low-frequency analyses. However, the simulation of SI and PI effects associated with high-speed systems requires more advanced techniques that are able to account for non-quasi-static field effects and deal with complex coupling mechanisms among many elements. General purpose numerical techniques, e.g. full-wave methods, have been used in the past for this purpose. Some examples are the finite difference time domain method (FDTD) [54], the partial equivalent electric circuit method (PEEC) [55], and the finite element method (FEM) [56]. Commercial tools that are based on the aforementioned techniques are widespread. Although full wave solvers provide the best flexibility to handle arbitrary geometries, the main disadvantage of these methods is that a full discretization of the model is required and therefore the computational burden rapidly grows as the operating frequency, size, and complexity of the interconnect structure increase.

For this reason, much effort has been expended to develop customized numerical or semi-analytical methods for analysis of multilayer substrates. Most of these approaches exploit the planar nature of the PDN [57]-[58], since the cavities, formed between adjacent reference planes, are in general very thin in comparison to the wavelengths of interest. Some of the techniques have been applied to the analysis of via transitions and power planes such as the multilayered finite-difference method (M-FDM) [59], the contour integral method (CIM) [60]-[62], the transmission matrix (TMM) [63] and transmission line matrix method (TLM) [64], multiple scattering methods [65]-[68], as well as analytical formulations [69]-[71].

The available methods can be further improved by offering higher flexibility and better system-level simulation capabilities, which is useful to enable the design, analysis, and pre-layout optimization of very complex structures at different levels of hierarchy (IC, package, board, system) and from different perspectives (SI, PI, EMC). It is also desirable to achieve these goals without the expenditure of massive

**Figure 2.7** General classification of available methods for high-frequency modeling of multilayer substrates.

computation. This demands more efficient and compact high-frequency interconnect models, and a better understanding of their applicability, limitations, and related techniques to compute their constituent elements.

In this vein, several hybrid techniques for analysis of complex multilayer structures, combining some of the aforementioned approaches, have also been proposed, for example in [72]-[77]. Segmentation techniques [60],[78] have been applied to describe multilayer power planes, and the modeling of traces connecting vias has been included using modal decomposition methods [79]. In fact, much of the work related to this thesis is a hybridization of diverse analytical and numerical techniques [19], where the co-simulation of SI, PI, and electromagnetic interference is also addressed [12],[17]. Figure 2.7 illustrates the different approaches mentioned above, classified in terms of computational efficiency and flexibility to handle arbitrary configurations and geometries.

## 3. Physical Effects Associated with Vias

As introduced in Chapter 2, multilayer substrates require the utilization of vias to interconnect signal traces and reference planes laid out at different levels. In contrast to the transmission line theory used to describe traces, the problem of via modeling is more complex due to its intricate environment [80]. These vertical interconnects act as discontinuities that couple signal and power nets, which lead to signal, power integrity, and other electromagnetic interference problems. Proper via design is therefore essential for interconnect systems capable of operating at Gb/s data rates [81].

At low frequencies, typically in the MHz range, quasi-static models are useful describing the behavior of vias [82]. However, at higher frequencies, the via currents excite parasitic modes between the reference planes, which are associated with wave propagation effects that cannot be captured with a quasi-static approach [54],[80]. Consequently, via modeling in the GHz range requires a good understanding of the underlying electromagnetic mechanisms.

In this chapter, the main physical effects associated with vias are reviewed, including the excitation of parallel-plate modes, the role of ground vias, and crosstalk. The extraction of transmission line parameters for vias, the influence of their geometry, and the stub effect are also discussed with the help of a set of generic examples.

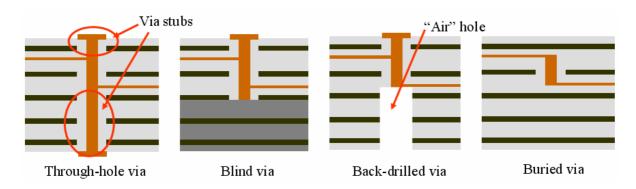

## 3.1. Types of Signal Vias

Common types of vias for utilization in multilayer substrates are illustrated in Figure 2.1. They are classified according to the topology of signal and reference levels that are part of the transition. A through-hole via (or simply thru) goes from side to side of the entire stackup. The via segment under or over stripline transitions is called via stub and it may insert unwanted resonances. This phenomenon is called the stub effect and it will be discussed in Section 3.6. Although the most commonly utilized due to its low fabrication cost, the thru configuration is detrimental in terms of crosstalk and because of the stub effect. For this reason, other types of vias can be fabricated at the cost of a more complex and expensive manufacturing process. A blind via passes through a section of the stackup and it is only visible from one board side. Thru vias can be

Figure 3.1 Common via types used in multilayer substrates.

converted to blind ones by removing their stub sections in a post-processing step known as back-drilling. Blind and buried vias, which only cross some of the internal cavities of the board, can also be fabricated with sequential processes (i.e. SBU, see Section 2.1).

The examples studied in this chapter illustrate thru via behavior; the basic structure is depicted in Figure 3.2. These were simulated with a full-wave solver utilizing the finite integration technique (FIT) in time domain [83].

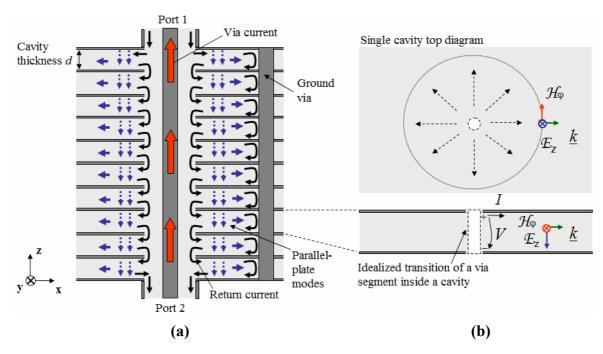

#### 3.2. Excitation of Parallel-Plate Modes

A typical via crosses many layers and the currents flowing on it, perpendicular to the signal and reference levels, can excite parasitic modes in the cavities formed between adjacent reference planes. They are called *parallel-plate modes*. Unlike conventional transmission lines, the return path for via currents is more complex and is influenced by the electromagnetic coupling between the plates and the number and position of return vias (Figure 3.2(a)).

Assuming that the via currents are uniformly distributed, the parallel-plate modes are, in principle, guided electromagnetic waves of cylindrical symmetry [84]. Because of the small separation between reference planes, it can also be assumed that only TEM waves are supported inside the cavities and that these fields are constant in the perpendicular direction (z-axis). Each cavity is then treated as a radial transmission line, with electromagnetic fields defined in cylindrical coordinates as [85]

$$\mathcal{E}_{z}(\rho,t) = A \cdot H_{o}^{(1)}(\underline{k}\rho) + B \cdot H_{o}^{(2)}(\underline{k}\rho), \qquad (3.1)$$

$$\mathcal{H}_{\varphi}(\rho,t) = \frac{j}{\eta} \cdot \left( A \cdot H_1^{(1)}(\underline{k}\rho) + B \cdot H_1^{(2)}(\underline{k}\rho) \right), \tag{3.2}$$

with  $H_n^{(1)}$ ,  $H_n^{(2)}$  the Hankel functions of order n, of first and second kind, respectively. The terms A and B comprise the complex amplitude and the harmonic time dependence of the inward and outward traveling waves, respectively,  $\underline{k} = \omega \sqrt{\mu \varepsilon}$  is the

**Figure 3.2** Illustration of parallel-plate modes excited by via transitions. (a) Signal and return path for the currents of a multilayer via. The return path is shared by the return vias and the reference planes, which can support propagating waves. (b) Definitions for a single via segment in a cavity, assuming infinite planes and neglecting the near field in the antipad region.

wave number, and  $\eta = \omega \mu / \underline{k} = \sqrt{\mu / \varepsilon}$  the wave impedance. The first term in Eqs. (3.1) -(3.2) represents radial waves traveling inward, whereas the second depicts outward traveling waves. If it is assumed that the reference planes extend to infinity, the inward traveling wave terms vanish. The terminal voltage and current for the radial transmission line are written as (Figure 3.2(b))

$$V = -\mathcal{E}_z \cdot d \,, \tag{3.3}$$

$$I = 2\pi r \cdot \mathcal{H}_{\varphi} . \tag{3.4}$$

The origin of the local coordinate system is defined at the via centers, with the radial coordinate  $\rho = (x^2+y^2)^{1/2}$ . Higher order TM and TE modes in z-direction inside the cavities could be also supported, however they have cutoff frequencies given by [54],[85]

$$f_c = \frac{n}{2d\sqrt{\mu\varepsilon}}$$

with  $n = 1, 2, 3, \dots$  (3.5)

with d the separation between power/ground plates. For a maximum frequency of 40 GHz and  $\varepsilon_r = 4$ , d must be larger than 70 mil to support the propagation of higher order modes. In practice, this separation –typically between 10 and 30 mil for high-speed PCBs– is often much smaller than the minimum wavelength of interest and it locates the cutoff frequencies of higher order modes far away (beyond 100 GHz). These evanescent modes, however, can influence the local via environment as it will be discussed next.

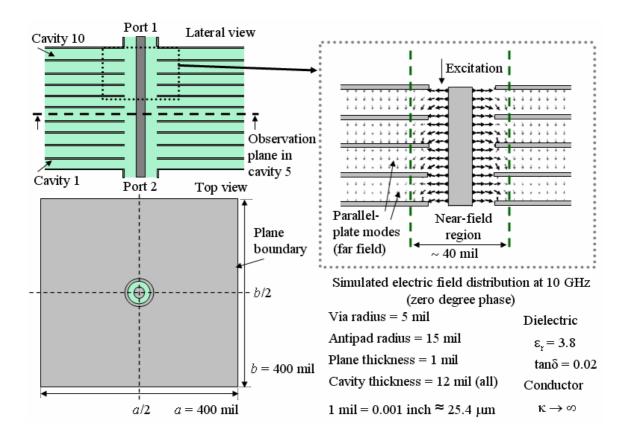

**Figure 3.3** Example of a multilayer via. The structure was simulated with the finite integration technique (FIT) [83] assuming perfectly matched layer (PML) boundaries at the board edges. The simulated electric field vector distribution on the cross section of the via shows the presence of parallel-plate modes and inhomogeneous fields in the antipad region. The excitation is a normalized Gaussian pulse ( $f_{max} = 40 \text{ GHz}$ ) applied to port 1.

The model for the full-wave simulation of a multilayer via is described in Figure 3.3. Initially, it is supposed that the planes are infinitely large, which means that there are no reflections coming from board edges and only outward traveling waves need to be considered. This condition is numerically modeled by an absorbing boundary condition (ABC) or perfectly matched layers (PML). Two wave ports are defined at both via ends and the excitation is a 1-(W) $^{0.5}$  Gaussian pulse with a maximum frequency content of 40 GHz. The time domain results are converted, in a post-processing step, into the frequency domain to get the field distributions and S-parameters. The coaxial extensions on via sides are necessary to provide a regular cross-section for the wave ports in the full-wave simulation.

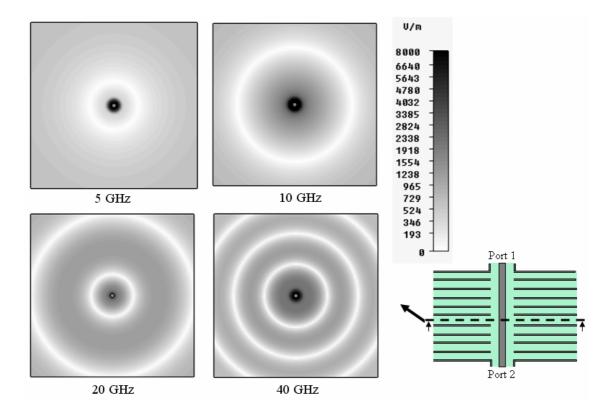

The numerical field simulation in Figure 3.3 shows the excitation region where the parallel-plate modes start to develop. Figure 3.4 illustrates the cylindrical nature of the parallel-plate waves by plotting the magnitude of the electric field inside the fifth cavity at different frequencies. The excitation was applied at the port number one, located at the top side of the via.

**Figure 3.4** Magnitude of the electric field inside the fifth cavity of the structure in Figure 3.3, for zero degree phase and assuming PML boundary condition at the board edges. The plots show the simulated cylindrical waves guided between two reference planes at different frequencies. The excitation is applied to port 1 and the fields are plotted on a logarithmic scale.

The vector field pattern in Figure 3.3 also indicates that an inhomogeneous field region exists near the via barrel and the antipad region, which has a diameter of about 40 mil in the case shown. These near fields can be related to the non-propagating modes inside the cavities. Their effect can be approximated with lumped capacitances for many practical situations (see Section 4.4). Near-field coupling is possible for vias in very close proximity or for vias sharing the same antipad such as differential ones.

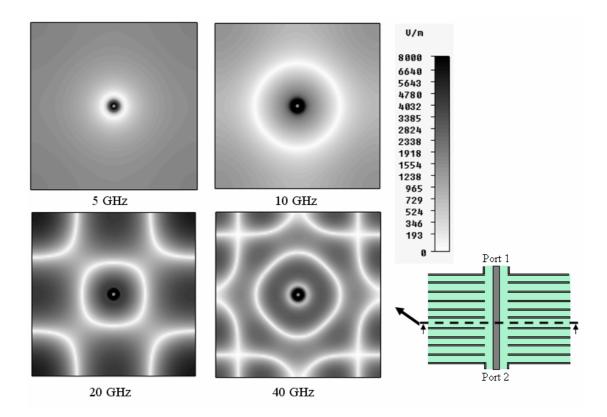

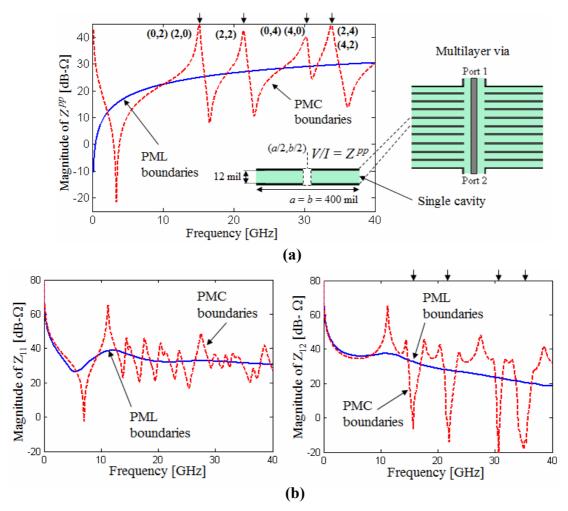

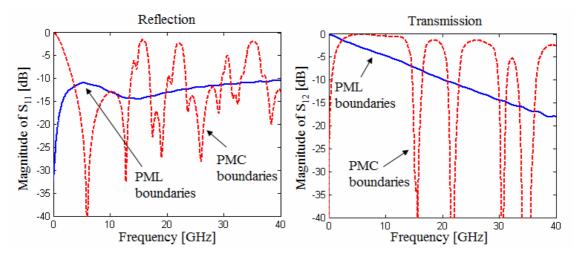

For finite planes, outgoing waves are reflected at the board edges. An open boundary condition, also denoted as perfect magnetic conductor (PMC), usually serves as a good approximation given the small separation between the planes. However, at higher frequencies, particularly for low loss and thick cavities, the final impedance of the space surrounding the board edges may become important and lead to a considerable amount of radiated emissions [17]. The plots in Figure 3.5 show the resultant electric field distribution in presence of ideal reflective open boundaries. The patterns describe resonant modes that are a function of the board geometry, material parameters, port location, and frequency. For a pair of rectangular plates, the resonant frequencies of the modes are given by [86]:

**Figure 3.5** Magnitude of the electric field inside the fifth cavity of the structure in Figure 3.3, for zero degree phase and assuming ideal open boundaries (PMC) at the board edges. The plots show the field patterns in presence of reflective boundaries at different frequencies. The excitation is applied to port 1 and the fields are plotted on a logarithmic scale.

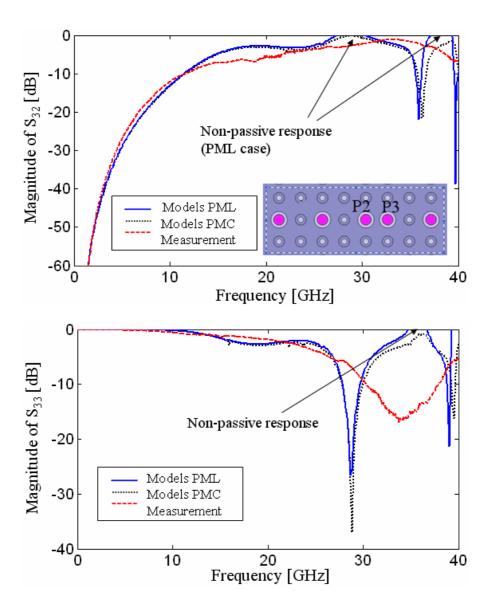

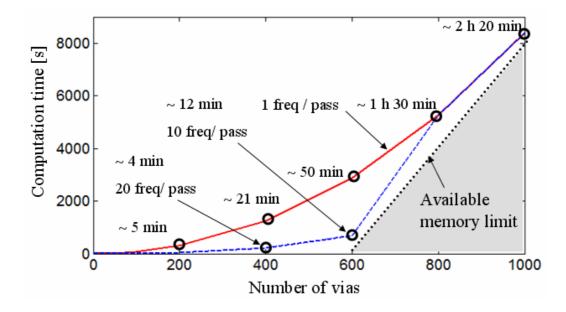

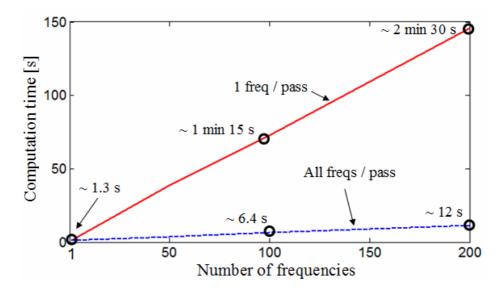

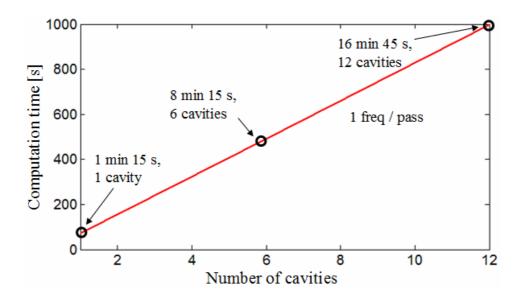

$$f_c = \frac{1}{2\sqrt{\mu\varepsilon}} \sqrt{\left(\frac{m}{a}\right)^2 + \left(\frac{n}{b}\right)^2}$$