# Bidirectional System on Chip for Intracorporeal Pressure Measurement

Vom Promotionsausschuss der Technischen Universität Hamburg-Harburg

zur Erlangung des akademischen Grades

Doktor-Ingenieur (Dr.-Ing.)

genehmigte Dissertation

Bryce T. Bradford

San Antonio, TX, USA

2014

- 1. Reviewer: Prof. Dr-Ing. Arne Jakob

- 2. Reviewer: Prof. Dr-Ing. Wolfgang Krautschneider

- 3. Reviewer: Prof. Dr.-Ing. Hoc Khiem Trieu

- Day of the defense: 25 November 2013

#### Abstract

A multichannel pressure sensing integrated circuit utilizing wireless power and wireless data transmission for long term monitoring of patients following endovascular stent implantation has been developed in partial fulfillment of the degree of Doctor of Engineering. Each of the 8 capacitance to digital converter signal conditioning chains is a fully differential architecture from signal input to the digital output sampled at 4ksps with  $3\mu$ W power consumption per channel. Power is supplied to the device using wireless radio frequency power transmission, and the signal conversion is performed using a single stage operational transconductance amplifier and a 10 bit fully differential charge redistribution ADC. The pressure sensing IC has integrated energy harvesting, power regulation, and wireless data interface electronics. =

To my loving wife, Stefanie, and my two wonderful daughters, Charlotte and Louisa.

### Acknowledgements

I would like to thank the heads of the TUHH Nanoelectronics department, Prof. Dr.-Ing. Wolfgang Krautschneider and Dr. Dietmar Schroeder, for their guidance for the duration of my doctoral studies. I want to thank all of my work colleagues who were always ready to offer help when needed. I would also very much like to thank the doctors from the University Clinic Hamburg-Eppendorf Radiology department, Director Prof. Dr. med. Gerhard Adam, Oberarzt Dr. med. Andreas Koops, and Dr. med Jan Buhk for their support and cooperation during this project work.

# Contents

| Li       | List of Figures vii |                  |                                                              |    |  |

|----------|---------------------|------------------|--------------------------------------------------------------|----|--|

| Li       | List of Tables xiii |                  |                                                              |    |  |

| G        | lossai              | ſy               |                                                              | xv |  |

| 1        | Intr                | oducti           | on                                                           | 1  |  |

|          | 1.1                 | Projec           | t Motivation                                                 | 1  |  |

|          | 1.2                 | Prelim           | inary Project Work                                           | 2  |  |

|          | 1.3                 | Propos           | sed Monitoring System                                        | 3  |  |

| <b>2</b> | Syst                | em O             | verview                                                      | 5  |  |

|          | 2.1                 | The R            | F Receive Block                                              | 5  |  |

|          | 2.2                 | Capac            | itance to Digital Converter                                  | 6  |  |

|          | 2.3                 | Data 🛛           | Fransmission                                                 | 7  |  |

|          | 2.4                 | Wirele           | ss Power Transmission                                        | 7  |  |

| 3        | The                 | $\mathbf{Press}$ | ure to Voltage Converter                                     | 9  |  |

|          | 3.1                 | Capac            | itance to Analog Conversion                                  | 10 |  |

|          |                     | 3.1.1            | Correlated Double Sampling with Input and Output Offset Cor- |    |  |

|          |                     |                  | rection                                                      | 10 |  |

|          |                     | 3.1.2            | Switched Capacitor Charge Injection                          | 11 |  |

|          |                     | 3.1.3            | Calculating $C_f$                                            | 15 |  |

|          |                     | 3.1.4            | The Final CDS Network Design                                 | 18 |  |

| 4        | The                 | Capa             | citance to Digital Converter Noise Analysis                  | 19 |  |

|          | 4.1                 | Genera           | al Transconductance Device Behavior                          | 20 |  |

### CONTENTS

|   | 4.2 | SC Noise Analysis                                | 23       |

|---|-----|--------------------------------------------------|----------|

|   | 4.4 |                                                  | 24       |

|   |     |                                                  | 24<br>28 |

|   |     |                                                  |          |

|   |     | 1                                                | 32       |

|   |     |                                                  | 34       |

|   | 4.3 |                                                  | 37       |

|   |     | 4.3.1 Noise Factor Derivation                    | 10       |

|   | 4.4 | The Folded Cascode Device Sizing                 | 14       |

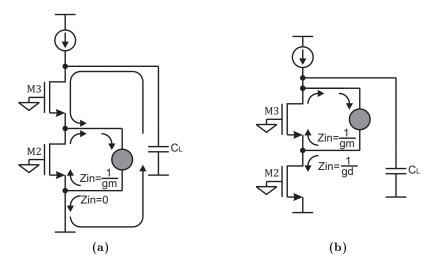

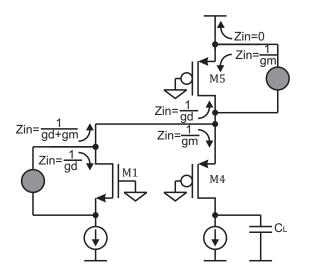

| 5 | The | e Gain Boosted Folded Cascode Amplifier Design 4 | 9        |

|   | 5.1 | Enhancing the Amplifier Gain                     | 50       |

|   |     | 5.1.1 The Cascode Load                           | 51       |

|   |     | 5.1.2 Quantifying the Gain Enhancement           | 55       |

|   | 5.2 | Gain Booster Stability                           | 56       |

|   | 5.3 |                                                  | 56       |

|   |     | -                                                | 57       |

|   |     |                                                  | 59       |

|   |     | 5.3.3 Gain Boosted Network Noise Current         | 50       |

|   | 5.4 | Switched Capacitor Networks                      | 51       |

|   | 5.5 |                                                  | 52       |

|   |     |                                                  | 37       |

|   | 5.6 | I G                                              | 58       |

|   | 5.7 |                                                  | 70       |

|   |     |                                                  |          |

| 6 |     | 5 5 5                                            | '3       |

|   | 6.1 | ADC Unit Cell Capacitor                          | 74       |

|   | 6.2 | ADC Unit Cell Mismatch                           | 75       |

|   |     | 6.2.1 ADC Unit Cell Distance Mismatch            | 76       |

|   |     | 6.2.2 ADC Unit Cell Mismatch from Device Area    | 77       |

|   |     | 6.2.3 Sizing the ADC Unit Cell                   | 79       |

|   | 6.3 | Passive Fully Differential ADC Conversion        | 34       |

|   |     | 6.3.1 The Charge Redistribution Block            | 34       |

|   |     | 6.3.2 ADC Capacitor Array LSB Charge Sharing     | 86       |

|   | 6.4 | Comparator with Offset Cancellation              | 38       |

#### CONTENTS

|   |     | 6.4.1    | The Comparator Preamplifier                         |

|---|-----|----------|-----------------------------------------------------|

|   |     | 6.4.2    | Comparator Input Offset Cancellation                |

|   |     | 6.4.3    | The Clocked Comparator                              |

|   |     | 6.4.4    | The Comparator Input Offset Cancellation Routine 95 |

|   |     | 6.4.5    | Minimizing the ADC Power Consumption                |

|   |     | 6.4.6    | ADC Performance Measurements                        |

| 7 | Wir | eless ]  | Power Transmission 101                              |

|   | 7.1 | The C    | Class E Power Amplifier                             |

|   |     | 7.1.1    | Designing and Tuning the Power Amplifier            |

|   | 7.2 | Outpu    | t Load Impedance Matching and Filtering             |

|   |     | 7.2.1    | Output Impedance Matching                           |

|   |     | 7.2.2    | Output Low Pass Filtering                           |

|   |     | 7.2.3    | The Output Power Level                              |

|   | 7.3 | The P    | Power Transmitting Antenna                          |

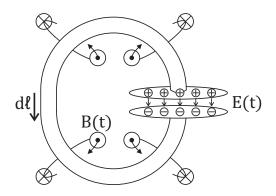

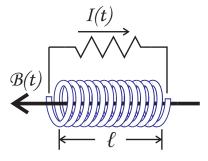

|   |     | 7.3.1    | Current Carrying Wire Loop                          |

|   |     | 7.3.2    | The Antenna                                         |

|   |     | 7.3.3    | Antenna Impedance Matching                          |

|   |     | 7.3.4    | Choosing the Transmission Frequency                 |

|   | 7.4 | The P    | Power Receiving Antenna                             |

|   |     | 7.4.1    | Choosing the Implant Inductor                       |

|   | 7.5 | Maxir    | nizing the Power Transmission Efficiency            |

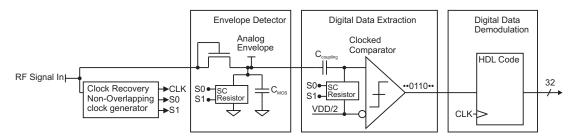

| 8 | Wir | eless ]  | Data Reception 123                                  |

|   | 8.1 | Wirele   | ess RX Electronics                                  |

|   |     | 8.1.1    | Envelope Detection                                  |

|   |     | 8.1.2    | The Clocked Comparator                              |

|   |     | 8.1.3    | Digital Data Demodulation                           |

|   |     | 8.1.4    | The Implant Configuration Registers                 |

| 9 | Wir | reless l | Data Transmission 135                               |

|   | 9.1 | The P    | Phase Locked Loop                                   |

|   |     | 9.1.1    | The Self Biased $\omega_n$                          |

|   |     | 9.1.2    | The Self Biased $\zeta$                             |

### CONTENTS

| 9.2   | 2 The P   | The PLL Control Blocks                                                                         |  |

|-------|-----------|------------------------------------------------------------------------------------------------|--|

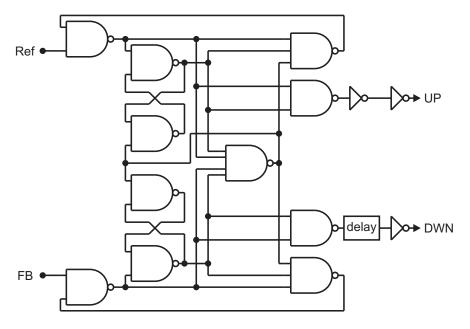

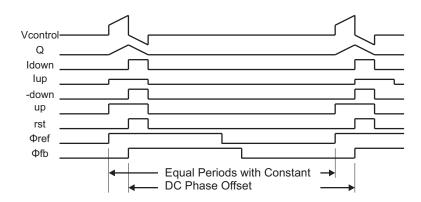

|       | 9.2.1     | The Phase Frequency Detector                                                                   |  |

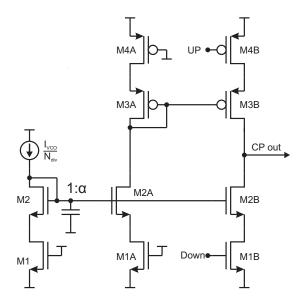

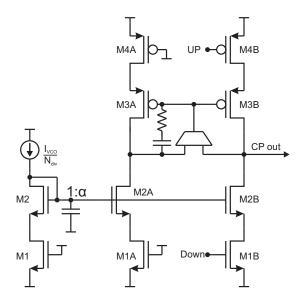

|       | 9.2.2     | The Charge Pump                                                                                |  |

|       | 9.2.3     | The Divide by N Current Mirror                                                                 |  |

|       | 9.2.4     | The Loop Filter                                                                                |  |

|       | 9.2.5     | Replica Bias Feedback Regulator                                                                |  |

|       | 9.2.6     | The Phase Forwarding Ring Oscillator                                                           |  |

|       | 9.2.7     | The Extended Modulus Divider                                                                   |  |

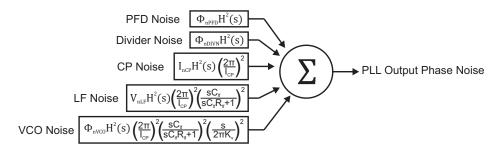

| 9.3   | The P     | LL Phase Noise Analysis                                                                        |  |

|       | 9.3.1     | The Digital Gate Noise Sources                                                                 |  |

|       |           | 9.3.1.1 kT/C Gate Noise                                                                        |  |

|       |           | 9.3.1.2 4kT $\gamma gm$ Gate Noise                                                             |  |

| 9.4   | The P     | LL Control Block Phase Noise Contributions                                                     |  |

|       | 9.4.1     | The PFD Phase Noise                                                                            |  |

|       | 9.4.2     | The Charge Pump Phase Noise                                                                    |  |

|       | 9.4.3     | The Loop Filter Noise                                                                          |  |

|       | 9.4.4     | The VCO Phase Noise                                                                            |  |

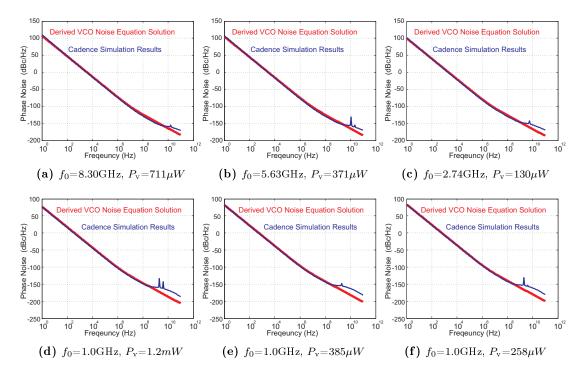

|       |           | 9.4.4.1 The VCO $1/f^2$ Phase Noise Content                                                    |  |

|       |           | 9.4.4.2 The VCO $1/f^3$ Phase Noise Content                                                    |  |

|       | 9.4.5     | The Divider Phase Noise                                                                        |  |

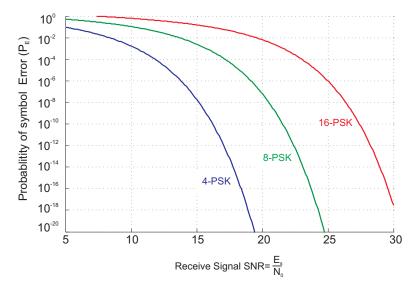

|       | 9.4.6     | RF Link Noise Budgeting                                                                        |  |

| 9.5   | 6 Meeti   | ng the noise requirements $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $178$ |  |

|       | 9.5.1     | The PFD and the Divider                                                                        |  |

|       | 9.5.2     | The VCO, Charge Pump, and Loop Filter                                                          |  |

| 10 Co | onclusio  | n 183                                                                                          |  |

|       | bliograph |                                                                                                |  |

|       | U 1       | •                                                                                              |  |

# List of Figures

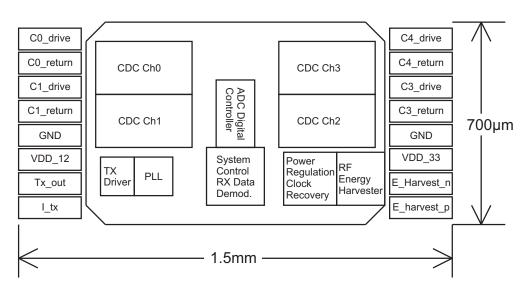

| 2.1  | The block diagram of the TIPS pressure measurement IC                                       | 6  |

|------|---------------------------------------------------------------------------------------------|----|

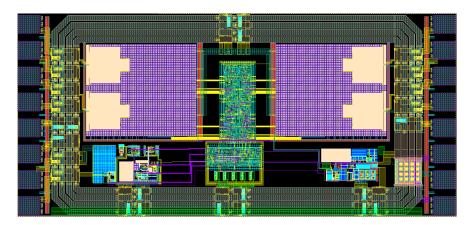

| 2.2  | The TIPS CHIP Layout                                                                        | 6  |

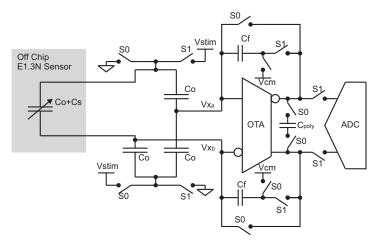

| 3.1  | The pressure sensing capacitance to digital conversion channel                              | 9  |

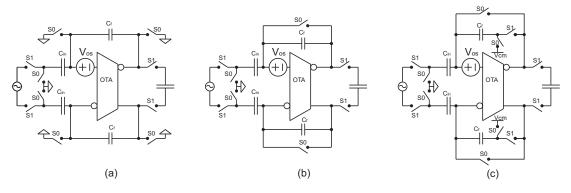

| 3.2  | Three different switched cap offset cancellation topologies                                 | 11 |

| 3.3  | Waveforms from simulations of the different CDS offset circuit                              | 12 |

| 3.4  | MOSFET charge injection                                                                     | 13 |

| 3.5  | Matched layout design                                                                       | 14 |

| 3.6  | The capacitive bridge signal voltage generation $\ldots \ldots \ldots \ldots \ldots \ldots$ | 15 |

| 3.7  | The CDS half circuit for finding the closed loop gain                                       | 17 |

| 4.1  | The MOSFET small signal model.                                                              | 20 |

| 4.2  | An equivalent circuit of a transconductance device.                                         | 21 |

| 4.3  | Input referred system noise current                                                         | 23 |

| 4.4  | Capacitance to digital conversion chain                                                     | 24 |

| 4.5  | Simplified circuit diagram of the SC amplifier in its two switch phases.                    | 25 |

| 4.6  | Schematic of the SC amplifier during phase S0                                               | 25 |

| 4.7  | Equivalent schematic for deriving the phase S1 feedback factor $(4.22)$ .                   | 27 |

| 4.8  | Schematic of the SC amplifier during phase S1                                               | 29 |

| 4.9  | Feedback Factor $gm$ reduction                                                              | 29 |

| 4.10 | The circuit used to determine the OTA effective output capacitance $C_{leff}$ .             | 31 |

| 4.11 | The OTA output settling characteristics                                                     | 35 |

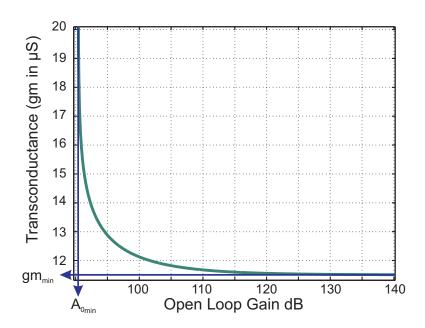

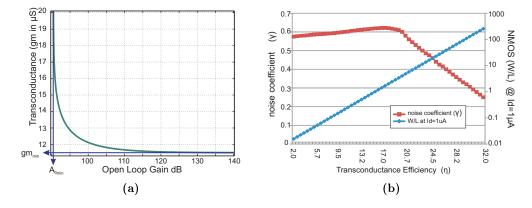

| 4.12 | Plot of gm versus $A_0$                                                                     | 37 |

| 4.13 | The folded cascode amplifier without the gain boosting amplifiers. $\ldots$                 | 38 |

| 4.14 | Cascode load noise circuits                                                                 | 38 |

#### LIST OF FIGURES

| 4.15 | The input and P-type load noise analysis.                                       | 39 |

|------|---------------------------------------------------------------------------------|----|

| 4.16 | Input referred system noise current                                             | 41 |

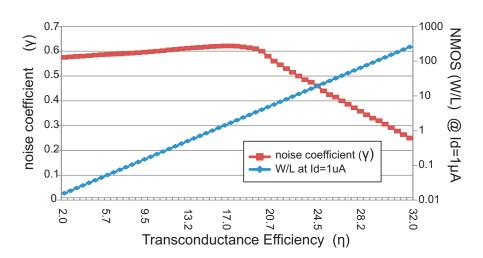

| 4.17 | Noise coefficient $\gamma$ and the device $\frac{W}{L}$ ratio at $I_d = 1\mu A$ | 43 |

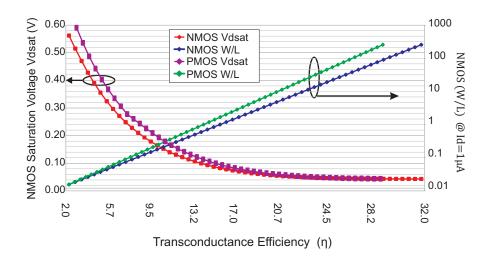

| 4.18 | MOSFET device saturation voltage and W/L ratio versus the $\eta_{gm}$           | 45 |

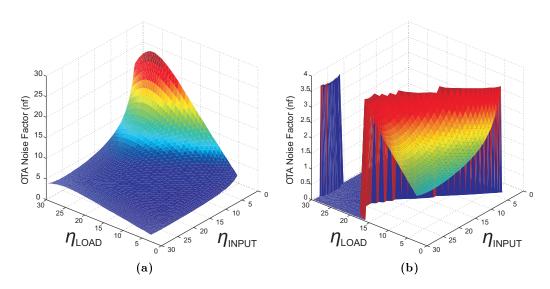

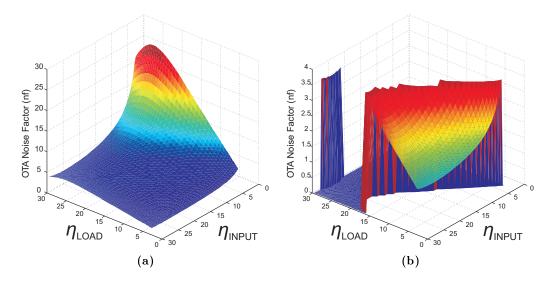

| 4.19 | 3D plot of the OTA noise factor solutions                                       | 46 |

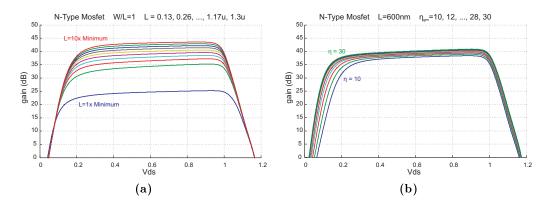

| 5.1  | Simulations for characterizing the MOSFET intrinsic gain $gmr_0$                | 50 |

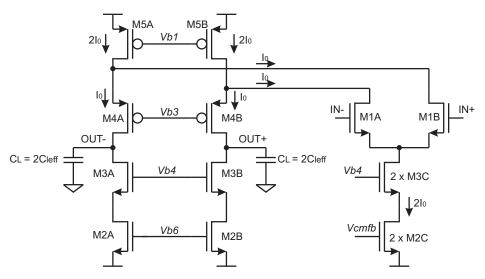

| 5.2  | The folded cascode amplifier without the gain boosting amplifiers. $\ldots$     | 51 |

| 5.3  | The cascode equivalent circuit for small signal impedance derivation $\dots$    | 52 |

| 5.4  | The gain boosted OTA.                                                           | 54 |

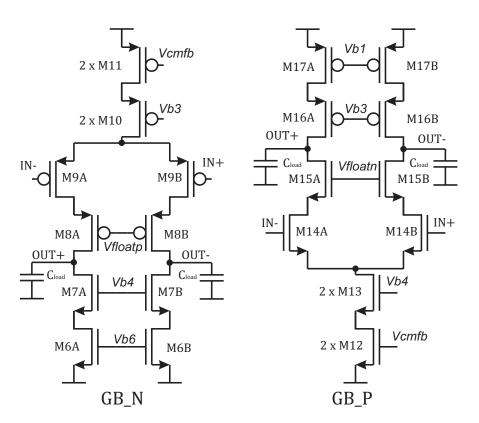

| 5.5  | The gain boosting amplifiers for the P and N type cascode load networks.        | 57 |

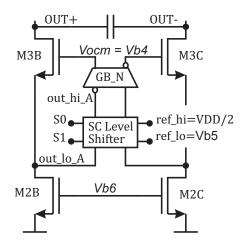

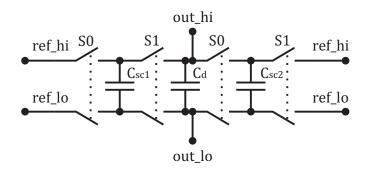

| 5.6  | The SC shifter applies a DC shift from M2's drain to GB_N's input               | 57 |

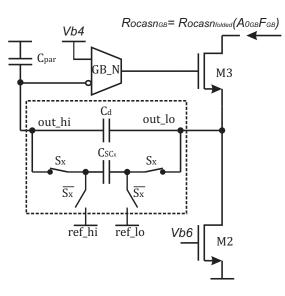

| 5.7  | A single channel of the SC level shifter network used in Fig. 5.6               | 58 |

| 5.8  | Half circuit for determining the gain boosted cascode feedback factor $\ .$     | 58 |

| 5.9  | The gain boosted cascode half circuit.                                          | 60 |

| 5.10 | SC level shifter floating bias generators.                                      | 62 |

| 5.11 | The SC common mode feedback voltage generator.                                  | 62 |

| 5.12 | Simulation data for choosing $gm,A_0,{ m and}{ m the}{ m W/L}$ ratios           | 65 |

| 5.13 | Plots for choosing the $\eta_{gm}$ values for $nf$                              | 65 |

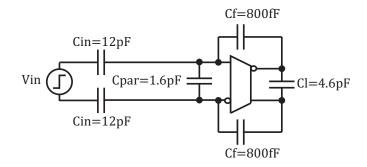

| 5.14 | Gain boosted OTA simulation test circuit                                        | 70 |

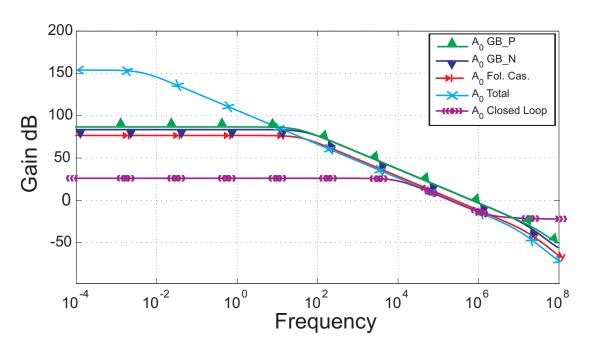

| 5.15 | Small signal analysis plots of the various system amplifiers.                   | 71 |

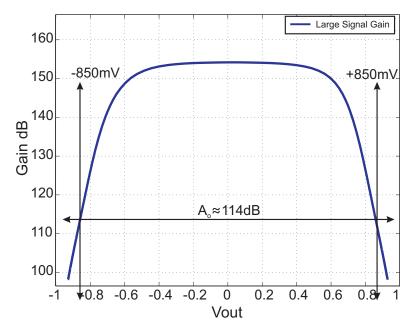

| 5.16 | Large signal gain DC sweep                                                      | 71 |

| 5.17 | The OTA step response                                                           | 72 |

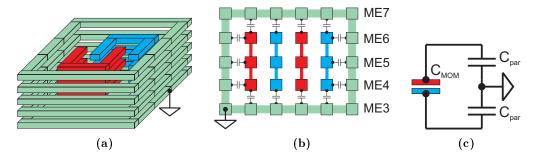

| 6.1  | The fully differential ADC unit cell capacitor.                                 | 75 |

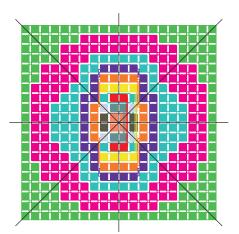

| 6.2  | The ADC layout                                                                  | 75 |

| 6.3  | ADC capacitor array common centroid layout                                      | 77 |

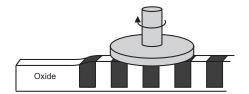

| 6.4  | Mismatch from chemical mechanical polishing                                     | 77 |

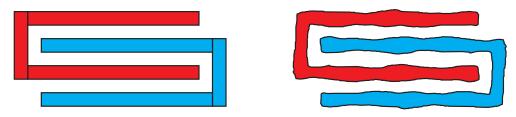

| 6.5  | Edge roughness in fabricated structures                                         | 78 |

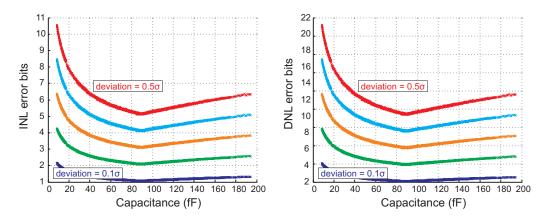

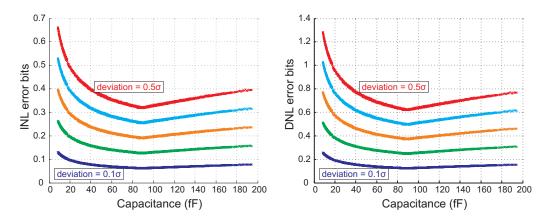

| 6.6  | Matlab simulations solving for worst case INL and DNL                           | 81 |

| 6.7  | Matlab simulations solving for worst case INL and DNL                           | 83 |

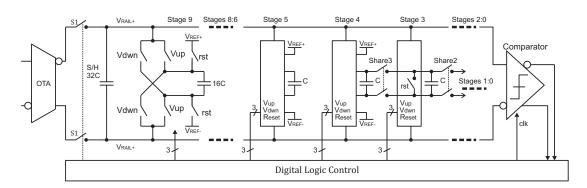

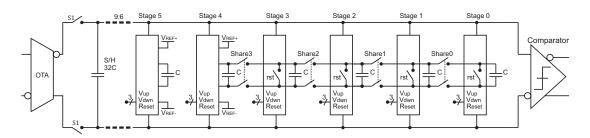

| 6.8  | SAR charge redistribution switching array.                                      | 85 |

| 6.9  | The ADC capacitor charge redistribution block                                   | 85 |

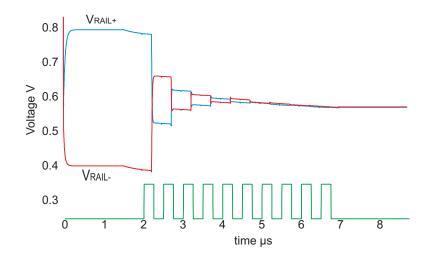

| 6.10 | Spectre post layout ADC simulation results.                                     | 87 |

| 6.11       | The charge sharing blocks                                                     | 88  |

|------------|-------------------------------------------------------------------------------|-----|

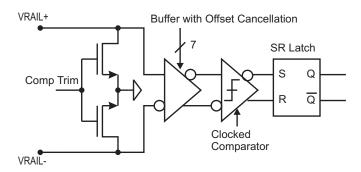

| 6.12       | The ADC comparator block                                                      | 88  |

| 6.13       | The comparator preamplifier buffer schematic                                  | 89  |

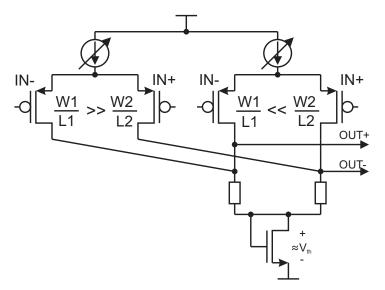

| 6.14       | The comparator preamplifier buffer kick-back reduction                        | 90  |

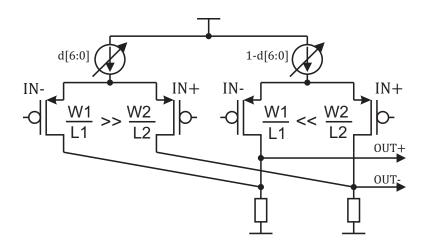

| 6.15       | The buffer amplifier offset cancellation current steering circuit. $\ldots$ . | 92  |

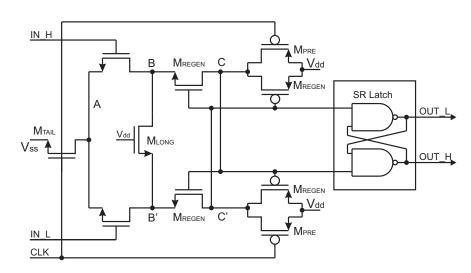

| 6.16       | The StrongARM latched comparator                                              | 93  |

| 6.17       | The ADC's low hysteresis StrongARM based latched comparator                   | 94  |

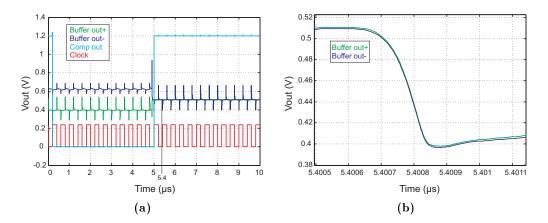

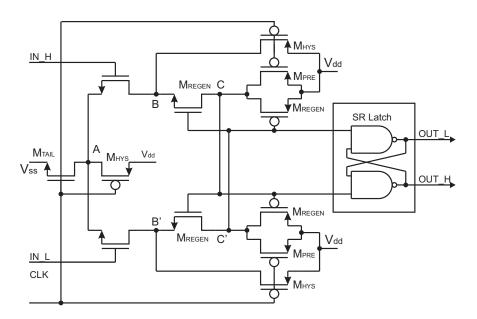

| 6.18       | The comparator block propagation delay                                        | 94  |

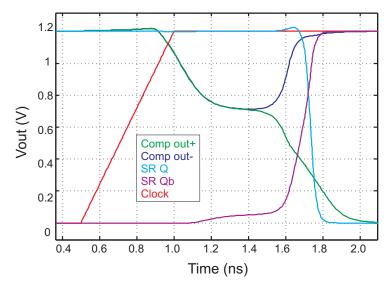

| 6.19       | The measured comparator offset cancellation routine                           | 96  |

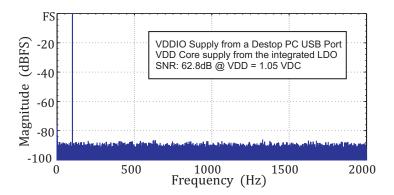

| 6.20       | The ADC conversion zero input noise spectrum                                  | 98  |

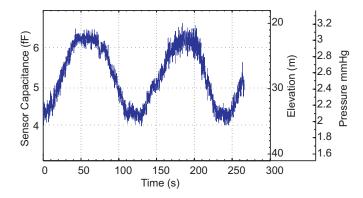

| 6.21       | The capacitive pressure sensor "Elevator Test" results                        | 99  |

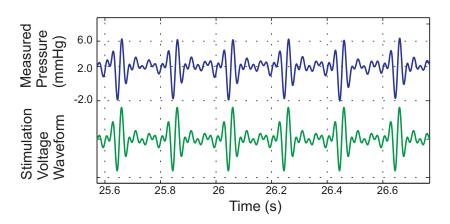

| 6.22       | The capacitive pressure sensor "Subwoofer Test" results                       | 99  |

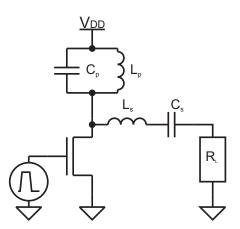

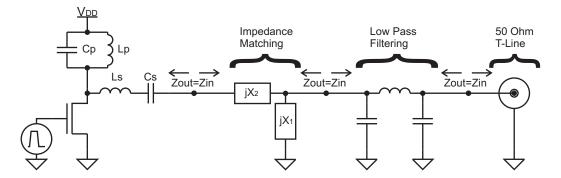

| 7.1        | The class E power amplifier architecture used in this project.                | 103 |

| 7.1        | Class E amplifier impedance matching and low pass filtering.                  | 105 |

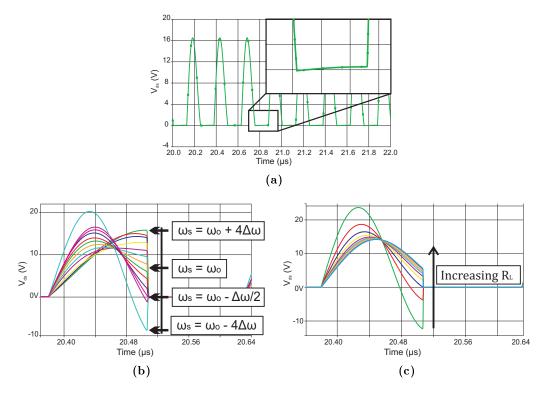

| 7.2        | $V_{\rm ds}$ waveform for class E ZVS operation                               | 100 |

| 7.3        | -                                                                             |     |

| 7.4        | Simplified diagram of the LC resonant power transmitter antenna.              |     |

| 7.6        |                                                                               |     |

| 7.0<br>7.7 | The series RLC circuit.                                                       |     |

| 7.8        |                                                                               |     |

| 7.8<br>7.9 |                                                                               |     |

|            | The wire loop antenna radiation resistance.                                   |     |

| 7.10       | The energy harvester solehold antenna                                         |     |

|            |                                                                               |     |

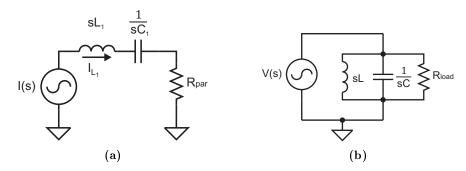

| (.12       | a) Series and b) Parallel RLC resonant circuits                               | 119 |

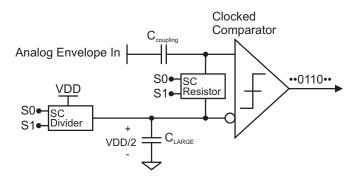

| 8.1        | The block diagram of the wireless data RX electronics                         | 123 |

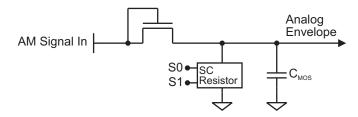

| 8.2        | The RX electronics envelope detector circuit.                                 | 125 |

| 8.3        | Envelope detection of an AM modulated signal                                  | 125 |

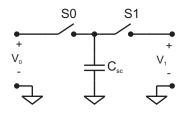

| 8.4        | The switched capacitor resistor                                               | 126 |

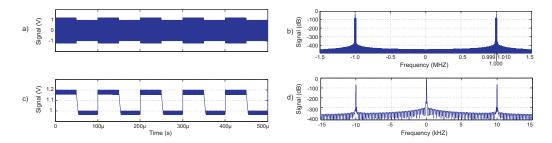

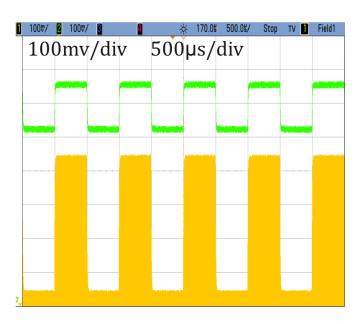

| 8.5        | The AM data demodulation envelope detector waveform                           | 128 |

| 8.6        | The RX signal clocked comparator with differentiating inputs                  | 128 |

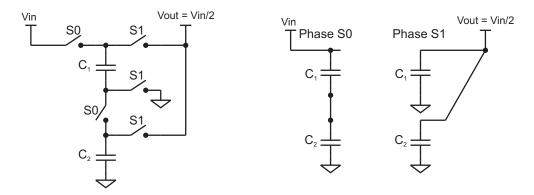

| 8.7        | The schematic of the SC capacitive divider circuit.                           | 129 |

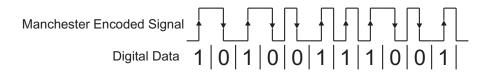

| 8.8        | RX byte modulation.                                                           | 131 |

|            |                                                                               |     |

### LIST OF FIGURES

| 8.9  | The RX data packet.                                                         | 131 |

|------|-----------------------------------------------------------------------------|-----|

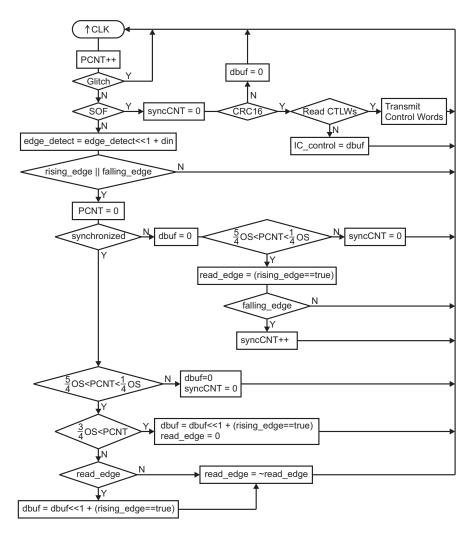

| 8.10 | The digital demodulation flow chart.                                        | 133 |

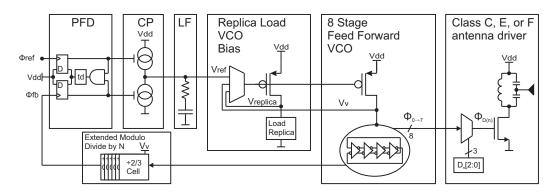

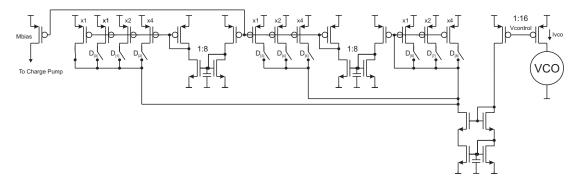

| 9.1  | The PLL circuit diagram                                                     | 137 |

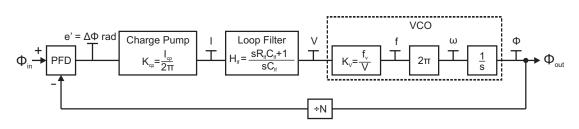

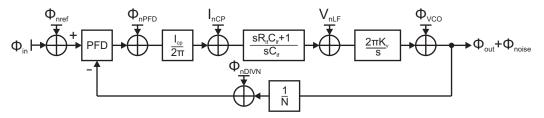

| 9.2  | The PLL block diagram                                                       | 138 |

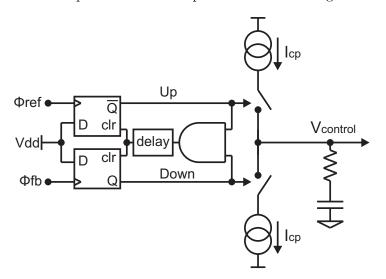

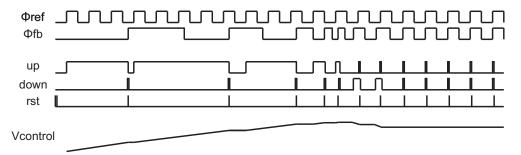

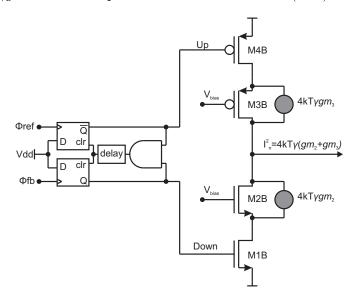

| 9.3  | The Phase Frequency Detector and Charge Pump Circuit.                       | 147 |

| 9.4  | The Phase Frequency Detector and Charge Pump timing diagram                 | 148 |

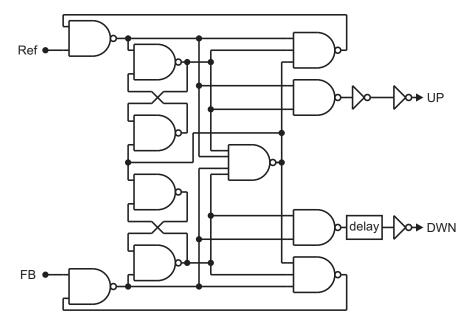

| 9.5  | The gate level PFD circuit.                                                 | 148 |

| 9.6  | The charge pump circuit.                                                    | 150 |

| 9.7  | The VCO control voltage effects from unequal charge pump current biasing    | 151 |

| 9.8  | The improved charge pump circuit with active branch current matching.       | 151 |

| 9.9  | The charge pump's inversely linear current reference mirror                 | 152 |

| 9.10 | The loop filter resistor.                                                   | 154 |

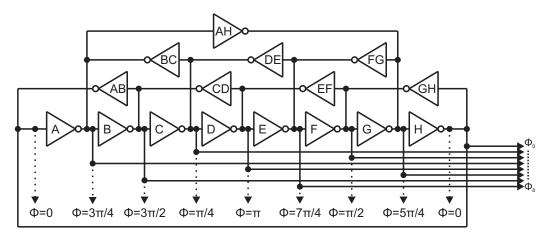

| 9.11 | The phase forwarding 8-stage ring oscillator                                | 155 |

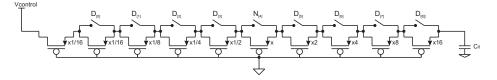

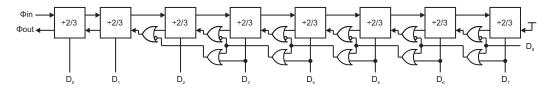

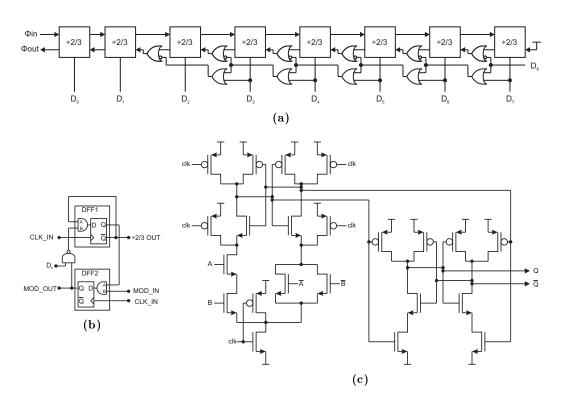

| 9.12 | The 6 stage, extended modulus $2/3$ divider block                           | 156 |

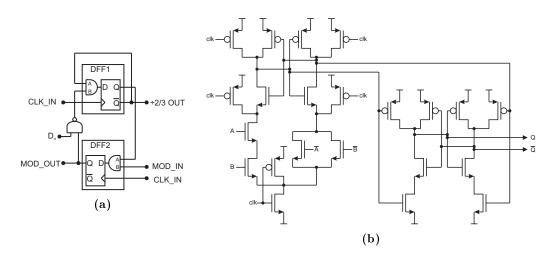

| 9.13 | The PLL divider divide by 2 or 3 cell                                       | 157 |

| 9.14 | The PLL block diagram                                                       | 157 |

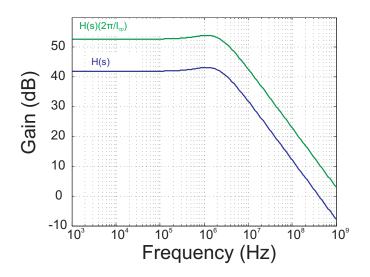

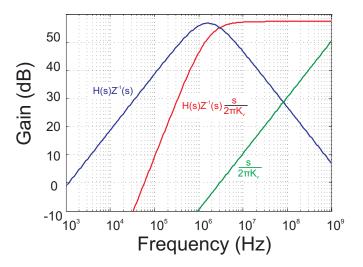

| 9.15 | The PLL source looking noise transfer functions $(9.29)$ through $(9.32)$ . | 159 |

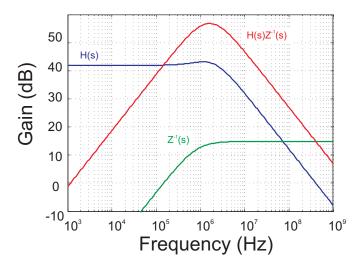

| 9.16 | The PLL loop filter noise transfer function.                                | 159 |

| 9.17 | The PLL VCO noise transfer functions.                                       | 160 |

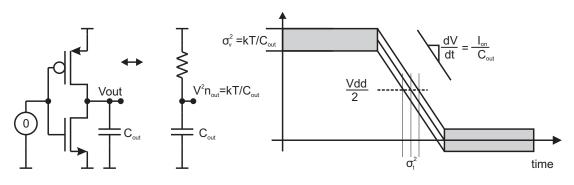

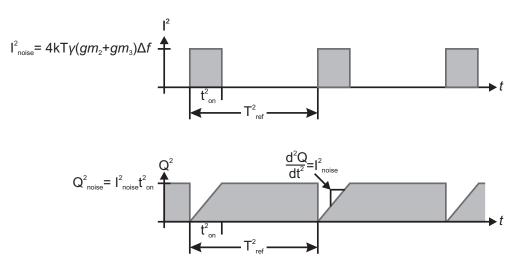

| 9.18 | The digital gate on or off state noise contribution                         | 161 |

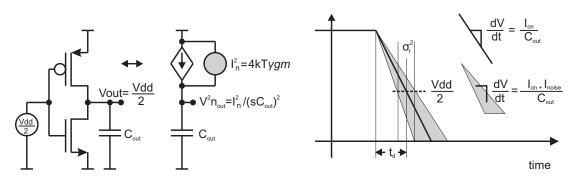

| 9.19 | The digital gate on or off state noise contribution                         | 163 |

| 9.20 | The gate level PFD circuit.                                                 | 165 |

| 9.21 | The charge pump schematic with noise sources.                               | 166 |

| 9.22 | The charge pump noise generation mechanism                                  | 167 |

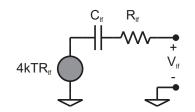

| 9.23 | The loop filter equivalent noise circuit                                    | 169 |

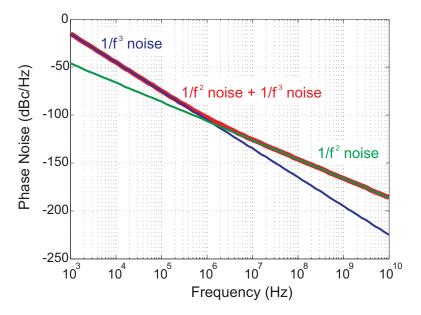

| 9.24 | The VCO phase noise composition.                                            | 170 |

| 9.25 | VCO noise simulation vs. derivation results                                 | 174 |

| 9.26 | The PLL Divider Circuit.                                                    | 175 |

| 9.27 | The probability of error for M-ary PSK                                      | 176 |

| 9.28 | The summation of the PLL phase noise sources                                | 178 |

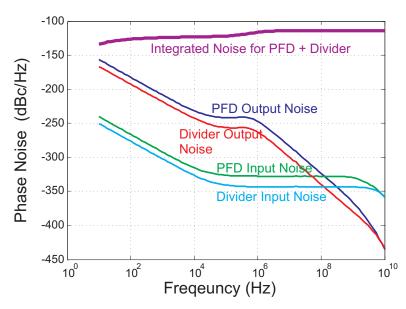

| 9.29 | The PLL output phase noise from the PFD and divider noise sources.          | 179 |

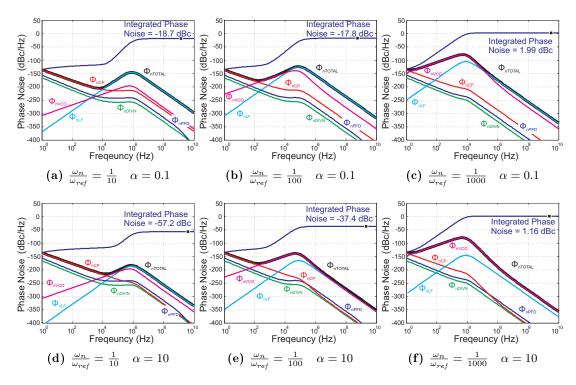

| 9.30 | PLL noise simulation results.                                               | 180 |

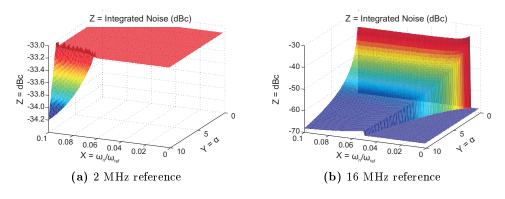

| 9.31 3D surface plot of PLL noise. |  | . 181 |

|------------------------------------|--|-------|

|------------------------------------|--|-------|

# List of Tables

| 5.1 | Pressure sensor system design constants               |

|-----|-------------------------------------------------------|

| 5.2 | Pressure sensor system $C_f$ and noise                |

| 5.3 | CDS system design values                              |

| 5.4 | Spectre noise analysis simulation results             |

| 5.5 | The OTA device parameters                             |

| 6.1 | Monte Carlo vs. Matlab simulation comparison          |

| 9.1 | PLL noise simulation results across varying bandwidth |

# Glossary

|                |                                                                                        | $\rm C_{ds}$   |

|----------------|----------------------------------------------------------------------------------------|----------------|

| $\eta_{ m gm}$ | $\eta_{\rm gm}=\frac{gm}{I_d}$ MOSFET transconductance efficiency                      | $C_{\rm oss}$  |

| ω              | Frequency in radians per second $\omega =$                                             | $C_{\rm v}$    |

|                | $2\pi f$                                                                               | F              |

| $\omega_o$     | Variable indicating center frequency<br>or resonant frequency in radians per<br>second |                |

|                |                                                                                        | $K_{\rm v}$    |

| $\sigma$       | Standard Deviation                                                                     | $R_r$          |

| $\sigma^2$     | Variance                                                                               | $R_{on}$       |

| au             | Exponential decay time constant                                                        | $T_o$          |

| f              | Frequency in Hertz                                                                     |                |

| $f_{ m t}$     | MOSFET intrinsic gain bandwidth product $f_{\rm t} = gm/C_{gs}$                        | $V_{ m dsat}$  |

| $f_{\rm v}$    | VCO frequency                                                                          | $V_{\rm ds}$   |

| $f_o$          | Variable indicating center frequency                                                   | $V_{\rm gs}$   |

|                | or resonant frequency in Hertz                                                         | $V_{\rm pp}$   |

| gd             | $gd = \frac{\partial Id}{\partial V_{\rm ds}}$ MOSFET output conductance               | $V_{\rm rms}$  |

| gm             | $gm = \frac{\partial Id}{\partial V_{\rm gs}}$ MOSFET transconduc-                     | $V_{ m v}$     |

|                | tance                                                                                  | $V_{os}$       |

| k'             | $\frac{\mu_o C_{\text{ox}}}{2n} \frac{W}{L}$ the MOSFET manufactur-                    |                |

|                | ing constants                                                                          | nf             |

| $k_{ m e}$     | The ratio of the RX electronics enve-                                                  | ADC            |

|                | lope detector cutoff frequency to the<br>AM carrier                                    | ADC            |

| $k_{ m m}$     | The ratio of the AM message fre-                                                       | $\mathbf{atm}$ |

| ~m             | quency to the AM carrier                                                               | CAD            |

|                |                                                                                        |                |

| n             | The number of inductor wire loop<br>turns per unit length                                             |

|---------------|-------------------------------------------------------------------------------------------------------|

| $r_o$         | $r_o = \frac{1}{gd}$ MOSFET output resistance                                                         |

| s             | $s=j\omega$ Laplace transform variable                                                                |

| $A_{\rm cl}$  | $A_{\rm cl} = rac{V_{out}}{V_{in}}$ The closed loop gain                                             |

| $A_o$         | The open loop gain of an amplifier                                                                    |

| $C_{\rm dg}$  | MOSFET drain gate capacitance                                                                         |

| $C_{\rm ds}$  | MOSFET drain source capacitance                                                                       |

| $C_{\rm oss}$ | $C_{\rm oss} \approx C_{\rm ds} + C_{\rm dg}$ MOSFET output capacitance                               |

| $C_{\rm v}$   | VCO total capacitance                                                                                 |

| F             | The feedback factor, the amount of<br>output signal fed back to the gate in-<br>puts                  |

| $K_{\rm v}$   | VCO transfer function in $\frac{Hz}{V}$                                                               |

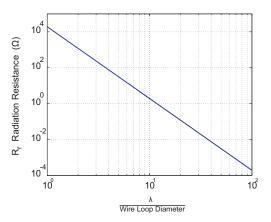

| $R_r$         | Antenna Radiation Resistance                                                                          |

| $R_{on}$      | The MOSFET on resistance                                                                              |

| $T_o$         | $V_{\text{out}} = V_{x_{ab}}T_o$ The amplifier loop transfer function                                 |

| $V_{ m dsat}$ | This is the $V_{\rm ds}$ voltage where the MOSFET transitions from linear to saturation               |

| $V_{\rm ds}$  | MOSFET drain to source voltage                                                                        |

| $V_{\rm gs}$  | MOSFET gate to source voltage                                                                         |

| $V_{\rm pp}$  | Voltage Peak to Peak                                                                                  |

| $V_{\rm rms}$ | $V_{\rm rms} = \frac{1}{\sqrt{2}} \left( \frac{V_{\rm pp}}{2} \right)$ This is the RMS signal voltage |

| $V_{\rm v}$   | VCO control voltage                                                                                   |

| $V_{os}$      | The OTA input referred offset volt-<br>age                                                            |

| nf            | OTA noise amplification factor                                                                        |

| ADC           | Analog to Digital Converter                                                                           |

| ADC           | Analog to Digital Converter                                                                           |

| atm           | Atmospheric pressure at sea level                                                                     |

Computer Aided Design

### LIST OF TABLES

| CDC                    | Capacitance to Digital Converter                                                   | NEB                     | Noise Equivalent Bandwidth, for 1 <sup>st</sup>                          |

|------------------------|------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------|

| CDC                    | Capacitance to Digital Converter                                                   |                         | order decay, NEB = $BW/4$ in rad/sec                                     |

| CDS                    | Correlated Double Sampling                                                         | ота                     | Operational Transconductance Am-<br>plifier                              |

| CML                    | Common Mode Logic<br>Chemical Mechanical Polishing                                 | ΟΤΑ                     | Operational Transconductance Am-<br>plifier                              |

| CRC                    | Cyclic redundancy check                                                            | PA                      | Power Amplifier                                                          |

| D                      | Duty Cycle of Switched Circuits                                                    | Ра                      | Pascal - Unit of pressure measure-                                       |

| dbuf                   | The RX data receive buffer                                                         |                         | $\mathrm{ment},1~\mathrm{atm}=101.325\mathrm{kPa}$                       |

| DFF                    | D Flip-Flop                                                                        | PDK                     | Process Design Kit                                                       |

| DNL                    | Differential Non-Linearity                                                         | PFD                     | Phase Frequency Detector                                                 |

| DR                     | $DR = 10^{\frac{6.02*N+1.76}{10}}$ For an N bit                                    | $\mathbf{PLL}$          | Phase Locked Loop                                                        |

|                        | ADC, this is the maximum signal en-                                                | $\mathbf{PLL}$          | Phase Locked Loop                                                        |

|                        | ergy versus the minimum step size<br>energy                                        | PSD                     | Power Spectral Density                                                   |

| $\mathbf{E}\mathbf{M}$ | Electromagnetic                                                                    | PSK                     | Phase Shift Keying                                                       |

| ENOB                   | $ENOB = \frac{SNR_{dB} - 1.76}{6.02}$ The effective number of bits                 | PSpice                  | Simulation Program with Integrated<br>Circuit Emphasis                   |

| ENOB                   | Effective number of bits                                                           | Q                       | Quality factor, the ratio of reactive<br>energy to resistive energy      |

| $\mathbf{ESR}$         | Electrostatic Resistance                                                           | RX                      | data reception                                                           |

| FOM                    | Figure of Merit                                                                    | $\mathbf{S}/\mathbf{H}$ | Sample and Hold capacitor                                                |

| $\mathbf{FS}$          | Full Scale is the maximum or min-<br>imum representative range of the<br>ADC       | SAR                     | Successive Approximation Register<br>ADC                                 |

| GBW                    | The gain bandwidth product                                                         | $\mathbf{SC}$           | Switched Capacitor                                                       |

| INL                    | Integral Non-Linearity                                                             | SEPIC                   | Single Ended Primary Inductor Con-<br>verter                             |

| KCL                    | Kirchoff's Current Law, the sum of<br>all currents into a node is equal to<br>zero | SNR                     | $SNR = rac{S^2_{ m ignal}_{rms}}{V^2_{ m noise}}$ Signal to noise ratio |

| KVL                    | Kirchoff's Voltage Law the sum of                                                  | $\mathbf{SNR}_{dB}$     | $SNR_{\rm dB} = 10 \log_{10}({ m SNR})$                                  |

|                        | all voltages around a loop is equal to                                             | $\mathbf{sps}$          | samples per second                                                       |

|                        | zero                                                                               | $\mathbf{SSB}$          | Single Sideband                                                          |

| $\mathbf{LSB}$         | Least Significant Bit                                                              | $\mathbf{T}\mathbf{X}$  | data transmission                                                        |

| $\mathbf{Mbps}$        | Megabits per second                                                                | Variance                |                                                                          |

| MOMcap                 | Metal Oxide Metal capacitor                                                        |                         | part of a signal (signal - average) $^2_{\rm rms}$                       |

| MOSFET                 | Metal Oxide Silicon Field Effect                                                   | VNA                     | Vector Network Analyzer                                                  |

| NT                     | Transistor                                                                         | WPT                     | Wireless Power Transmission                                              |

| Ν                      | Number of inductor wire loop turns                                                 | $\mathbf{ZVS}$          | Zero Voltage Switching                                                   |

## Introduction

Patients suffering from various types of cardiovascular disease will often undergo endovascular stent implantation. Afterwards, patients are generally required to have periodic checkups for the rest of their lives to verify that the stent implant is still functioning as expected. Today, these checkups require the patient to make a trip to the hospital to undergo computer imaging, sonography, MRI, or X-Ray computed tomography. These scans are then reviewed by a physician to verify the functionality of the stent implant.

#### 1.1 **Project Motivation**

The goal of this research work was to develop a system that not only improves the accuracy of the stent implant verification process by collecting direct real time pressure measurements at the location of the stent implant, but to allow these checkups to be performed from the comfort of the patient's home. With this new system, the patient would be able to take pressure measurements from the stent implant at any time of their choosing, and they could then send the data files to their physician for clinical evaluation.

The methods for determining stent implant efficacy are dependent on the purpose for which the stent was implanted. One major use for stent implants is the treatment of aortic aneurysms. The treatment of aneurysms requires the stent to fully prevent blood from leaking into the aneurysm sac. For this purpose, an array of sensors placed around the outside of the stent could be used to detect localized pressure gradients indicating blood leakage around the stent. Another common use for endovascular stents is to help

1

#### 1. INTRODUCTION

dilate arteries to improve blood flow. To determine if the artery is still being held open and allowing adequate blood flow, an array of sensors with good time and pressure resolution will be used to measure the blood flow through the stent to give warning if the artery once more starts to become blocked.

The device requirements set forth by the expected operating conditions are that the system needs to be able to measure absolute pressure from an array of sensors with a pressure resolution better than 1mmHg, and the system needs to sample fast enough to capture the leading edge of a wave travelling at roughly 1m/sec using sensors which are spaced only 1cm apart from each other. Also, because the device is intended for permanent implantation without the option of battery replacement, the whole system must consume a minimum of power to meet the energy supply constraints associated with wireless power transmission.

#### **1.2 Preliminary Project Work**

During the first half of this doctoral work, a proof of concept demonstrator was built and tested by way of in vivo animal testing at the University Clinic Hamburg-Eppendorf. The proof of concept demonstrator was constructed using commercially available electronics. The main controller was a 16 bit microcontroller with 4 ADC channels, and the sensors were micromachined piezoresistive pressure sensors. In December 2011, a successful round of animal testing was concluded giving proof of concept that the wireless power transmission and wireless data transmission design was valid.

Even though the demonstrator was able to show proof of concept, there were many qualities of the demonstrator which needed improvement. First and foremost was the active power consumption. When the demonstrator was active, and the piezoresistive pressure sensors were energized for pressure measurement, the system had an active power consumption of about 15mW, which is a tremendous amount of energy for only four pressure sensors. In addition to the power consumption, the resolution of the pressure sensors was only about 12 mmHg per least significant bit.

The design, construction, and testing of the proof of concept demonstrator will not be covered in this paper. Instead, this paper will cover the design of a new pressure measuring device capable of much greater pressure and time resolution at much lower energy requirements.

### 1.3 Proposed Monitoring System

This paper will present a system which is being designed to meet these requirements. The system uses an external RF energy sender which serves as the energy source for the pressure sensing implant. The pressure sensing implant has an array of capacitive pressure sensors which are measured with an application specific integrated circuit (ASIC). The ASIC has integrated wireless energy harvesting electronics, 4 capacitance to digital converter channels, and a wireless bi-directional communications interface. The system can simultaneously measure 4 different pressure sensors at 4ksps with a pressure resolution of 0.75mmHg, and transmit those pressure samples to an external monitoring device for display and data logging.

#### 1. INTRODUCTION

## System Overview

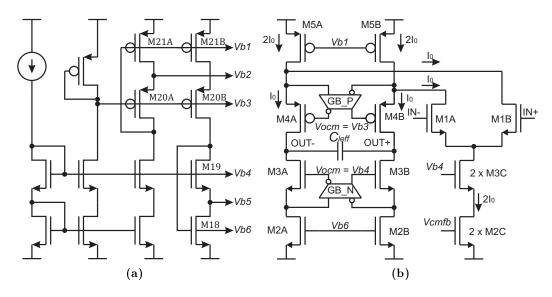

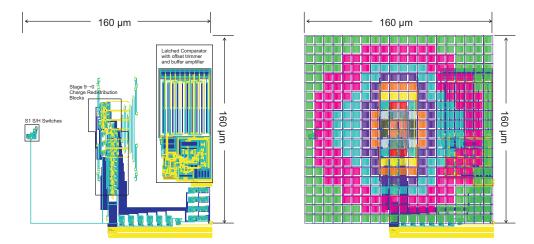

In February of 2012, design work began on a completely integrated system on chip which could combine all of the discrete elements of the demonstrator system into one silicon package. In November of 2012, the first design was completed and sent for fabrication, and in October of 2013, a second version of the chip was submitted for manufacture. It is the design of this fully integrated system on chip which will be presented in the paper.

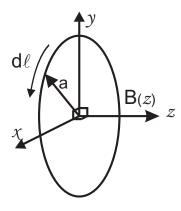

The pressure monitoring system is a complete mixed signal system on chip with RF energy collection, capacitance to digital conversion, bidirectional data communication, and a digital control logic block, Figs. 2.1. The implant has been designed to be permanently implanted inside the affected artery as an integrated part of the endovascular stent implant, and to receive its energy and transmit its pressure samples wirelessly to an external reader device.

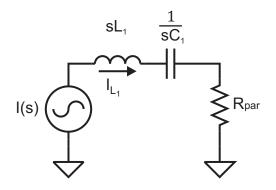

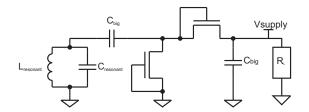

#### 2.1 The RF Receive Block

The RF receive block of the implant is made up of the energy harvester and clock recovery blocks, voltage regulation and power distribution, and receive data demodulation blocks. The energy harvester rectifies the RF energy and extracts the system clock. The voltage regulation and power distribution blocks generate the 1.2 VDC and the analog system bias reference currents. The receive data demodulation blocks extract the analog data envelope from the AM modulated RF energy carrier.

$\mathbf{2}$

Figure 2.1: The block diagram of the TIPS pressure measurement IC.

Figure 2.2: The layout of the TIP pressure measurement IC in 130nm UMC technology.

### 2.2 Capacitance to Digital Converter

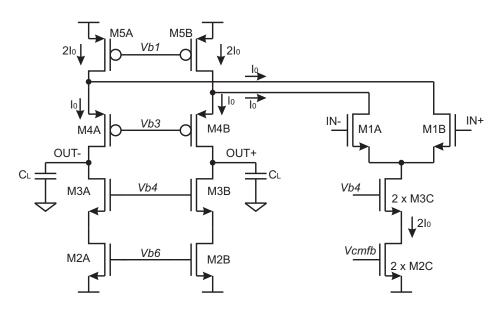

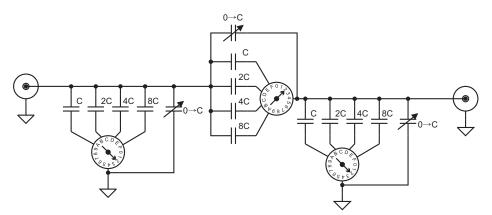

The implant has 4 integrated capacitance to digital conversion (CDC) channels. Each channel uses a capacitive bridge architecture to generate the signal, and an operational transconductance amplifier (OTA) to amplify the small signal from the capacitive bridge to the full scale signal for the digital conversion. The digital conversion is accomplished using a fully differential analog to digital converter (ADC).

#### 2.3 Data Transmission

Using the extracted clock as a reference, a phased locked loop (PLL) is used to generate a high frequency RF data carrier which is an integer multiple of the RF energy carrier. The PLL is a highly configurable self biasing design which can be operated over a wide range of oscillation frequencies. This gives it the ability to transmit its data using any of the various RF spectrum energies which are available for medical devices [1, 2].

#### 2.4 Wireless Power Transmission

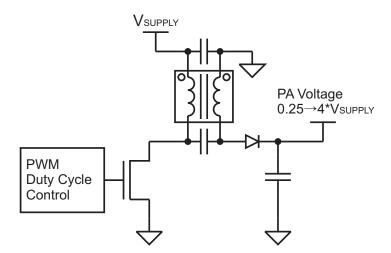

To enable permanent implantation without the capability of changing batteries at a later date, the implant uses RF energy harvesting as its energy source. The RF power sender is a class E tuned amplifier, and it serves both as the implant's energy source and clock source. The power sender and the implant are coupled together through resonant magnetic coupling.

The various chapters in this dissertation will be dedicated to giving an in depth description of the method and performance of each of these system design blocks.

### 2. SYSTEM OVERVIEW

## 3

## The Pressure to Voltage Converter

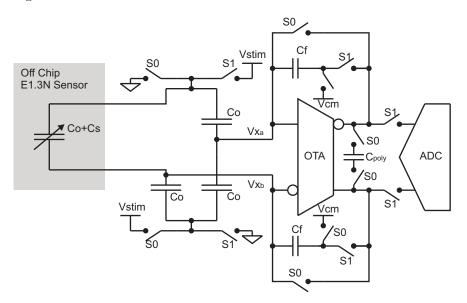

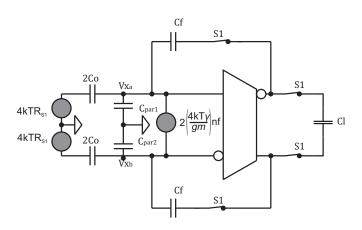

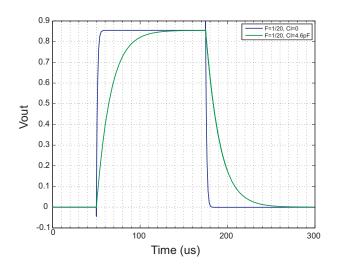

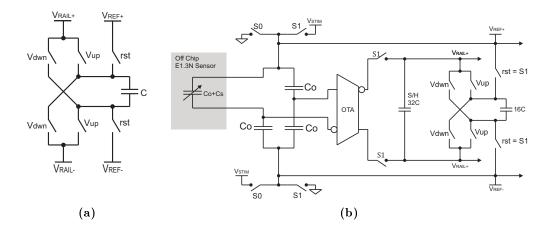

The ASIC design developed during this research work is, first and foremost, a pressure sensing IC. There are 4 pressure sensing channels working in parallel to simultaneously measure blood pressure at a combined rate of 16,000 samples per second (sps). The implant's IC design has been built in a 130nm CMOS technology process, and it has been custom designed to measure a commercially available capacitive pressure sensor, the E1.3N from Protron Mikrotechnik [3]. Starting with the pressure sensitive capacitor, the pressure sensing channel in Fig. 3.1 measures the signal voltage from the capacitive bridge, amplifies the signal using a gain boosted operational transconductance amplifier (OTA), and converts the analog signal to a digital value with the 10 bit analog to digital converter.

Figure 3.1: The pressure sensing capacitance to digital conversion channel.

To accurately measure the sensor's capacitance, a complete signal conditioning chain for converting the sensor capacitance to an analog signal for the analog to digital converter (ADC) has been developed. The signal conditioning electronics have been designed with a special emphasis on meeting the ADC signal to noise (SNR) requirements while consuming the minimum amount of power possible.

#### 3.1 Capacitance to Analog Conversion

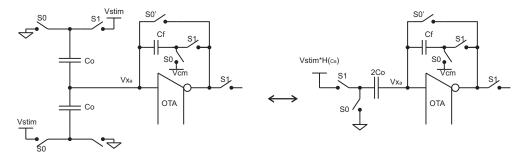

This chapter will describe a circuit architecture which measures the capacitor using correlated double sample techniques (CDS) [4, 5]. The correlated double sampling signal conditioning chain is used to generate a signal voltage from the pressure sensitive capacitor, and apply gain to that signal for analog to digital conversion. There are as many different switched capacitor (SC) gain stage structures as there are different ways to use them, but they all essentially behave the same way. Operating with two non-overlapping clock phases, S0 and S1, the OTA resets itself during phase S0, and it samples the input voltage during phase S1. Figure 3.1 shows the basic structure of the capacitance to digital converter chain which was used for this design.

#### 3.1.1 Correlated Double Sampling with Input and Output Offset Correction

The signal amplifier is a fully differential SC amplifier with input and output offset compensation (Fig. 3.1) [6]. The SC amplifier takes two input signal samples to generate one output voltage. During SC switch phase S0, the amplifier resets itself by placing itself in a unity gain configuration. While in unity gain, any input referred offset voltage  $V_{\rm os}$  shows up across the OTA's output and is inverted and fed directly back to the input because of the unity gain feedback. This action is called input offset cancellation.

During the S0 reset phase, a voltage equal but opposite to the OTA's input referred offset gets sampled across  $V_{ab}$ , and when the system switches to phase S1 the OTA behaves as if it were a perfect OTA with no input offset voltage. However, there is now an offset voltage which would be present at the OTA output if it is not taken care of. To cancel out the output offset voltage, during S0 when the input offset is being canceled, the right side plates of the feedback capacitors  $C_f$  (Figure 3.1) are set to the common mode voltage  $V_{cm}$ . This means that the offset voltage which gets stored across the output also gets stored across the feedback capacitors. Because the output offset has been stored across the feedback capacitors, when the right side plates are switched from ground to the output node, then the output nodes, which were previously at  $V_{os}$ , must swing to  $V_{cm}$  for  $V_{os}$  to be maintained across  $V_{x_{ab}}$ .

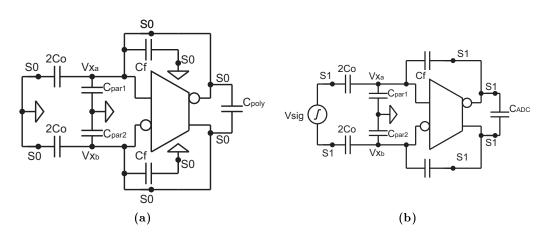

Figure 3.2: Three different switched capacitor gain stage offset cancellation topologies a) A CDS structure with no offset cancellation.

b) A CDS structure with only input offset cancellation.

c) A CDS structure with input and output offset cancellation.

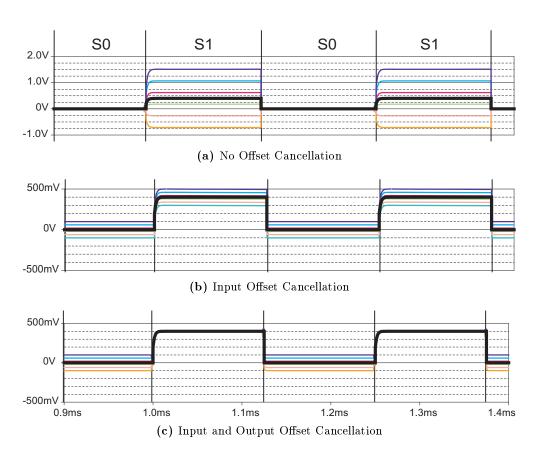

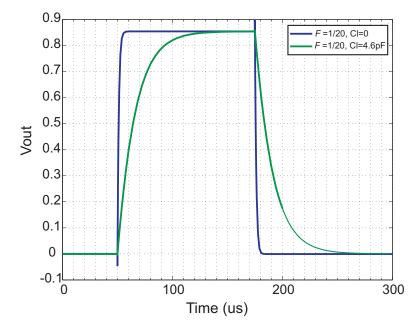

Fig. 3.3 shows three simulation runs, one simulation for each of the three circuits from Fig. 3.2. Each of the three simulations has an input signal voltage of  $V_{\rm in} = 40$ mV with a closed loop gain  $A_{\rm cl} = 10$  V/V, and the simulated input offset voltage is stepped from -100mv to +100mV in 40mV increments. Fig. 3.3a shows how the output voltage is the input signal plus the static DC offset multiplied by the closed loop gain. Fig. 3.3b shows how the output voltage has a constant offset equal to the input referred offset voltage. Fig. 3.3c shows that during the reset phase S0 there is an offset voltage at the output (this is the offset which is zeroing out the input offset), but during the sample phase S1 the output offset voltage is zeroed out, and the final output voltage is  $V_{\rm out} = V_{\rm in}A_{\rm cl} = 400$ mV

#### 3.1.2 Switched Capacitor Charge Injection

The CDC gain stage is a switched capacitor gain stage, and each of these switches are MOSFET switches. A MOSFET is great as an off switch with an off resistance on the order of several tens of gigaohms, but the transition from on to off has a deleterious side effect called charge injection.

#### **3. THE PRESSURE TO VOLTAGE CONVERTER**

Figure 3.3: Waveforms from simulations of the circuits given in Fig. 3.2. The desired output voltage is the bold trace  $V_{\text{out}_0} = V_{\text{in}}A_{\text{cl}}$ , and it is plotted against three different switched capacitor structures where the input offset voltage is stepped from -100mV to +100mV.

- a) With no input or output offset cancellation:  $V_{out} = A_{cl}(V_{in} + V_{os})$

- b) With only input offset cancellation:  $V_{\rm out} = A_{\rm cl} V_{\rm in} + V_{\rm os}$

- c) With input and output offset cancellation:  $V_{\rm out} = A_{\rm cl} V_{\rm in}$

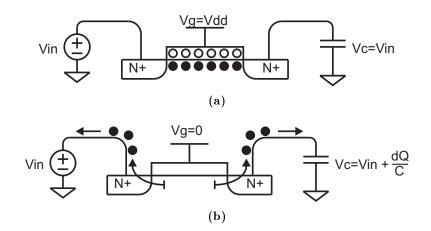

Figs. 3.4a and 3.4b shows the MOSFET as it switches from on to off. Charge injection into the low impedance voltage source causes no change in its voltage, but the effect of charge being injected onto the capacitor causes a voltage jump across C equal to (3.1).

$$dV = \frac{dQ}{C} \tag{3.1}$$

Charge injection is caused by the physical process of turning a MOSFET off, and as long as MOSFETs are used as the switches, there will be some charge injection. This project work did not attempt to develop a new way of building the switches. Instead,

Figure 3.4: MOSFET charge injection

this project work exploits the differential nature of the gain stage to minimize the effects of the charge injection.

The nodes which experience charge injection are nodes  $V_{x_{a,b}}$  and the right hand side plates of the feedback capacitor. During reset phase S0, the OTA inputs  $V_{x_a}$  and  $V_{x_b}$ , the right hand side feedback capacitor plates (Fig. 3.1), and the OTA output nodes are all reset to Vcm (this is accurate if  $V_{\rm cm} + V_{os} \approx V_{\rm cm}$ ). Because all of these nodes are at a known potential as the device switches from S0 to S1, then it is assumed that the amount of charge injected onto  $V_{x_a}$  and  $V_{x_b}$  are equal to each other and remain the same from sample to sample. This type of deterministic behavior lends itself well to the use of a fully differential architecture. If the amount of charge injected onto the two differential nodes is equal, then the differential voltage change will be negligible. Also, if the amount of charge injected onto the differential nodes is not equal, but is always the same from sample to sample, then this manifests itself into a constant offset voltage which can be calibrated out. The two switches on the  $C_f$  right hand side plate, S0 and S1, have been sized with equal width and length, so that the charge carriers which are injected onto the feedback capacitor plate by the S0 switch channel destruction, are then removed from the plate by the S1 switch channel creation.

Because each and every one of the nodes starts at a pre-determined S0 reset voltage, the most effective method for ensuring that the charge injection from the switches is common mode is to ensure that the complimentary switches on the top and bottom of the circuit are as closely matched to each other as possible when layed out on the IC.

#### 3. THE PRESSURE TO VOLTAGE CONVERTER

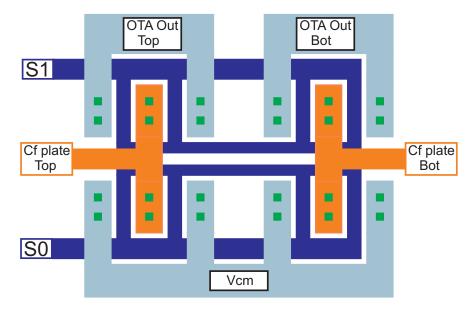

Fig. 3.5 shows the layout used for the two feedback capacitors,  $C_f$  in Fig. 3.1, and their S0 and S1 switches.

Figure 3.5: The layout design for minimizing mismatch between the complimentary switches of the SC amplifier.

Each of the switches are dual gate MOSFETS which helps to reduce the parasitic drain capacitance and to ensure that the current flows in both directions through each devices. The switches are layed out so that their spatial orientations are as closely matched as possible to try to accomplish as effective charge injection cancellation and matching as possible. The switches and capacitors are close to each other, and the capacitor and switch groupings are mirror images of each other.

The system has a relatively slow sample rate, which makes it fairly easy to size the switch transistors so that their on resistance  $R_{on}$  is small enough to not slow down the system response. The maximum output swing of the OTA is  $V_{dd}/2V_{dsat}$ , which is a little bit less than the NMOS threshold voltage. This has the effect of decreasing the NMOS  $R_{on}$  as the output nodes potential starts to put the MOSFET device into the linear region. But, because the required bandwidth of the system is relatively low, the result of increasing  $R_{on}$  does not have a significant impact on the switches response time. However, the switches which drive the capacitive bridge input signal generator are transmission gates to ensure good rail to rail voltage stimulation.

#### 3.1.3 Calculating $C_f$

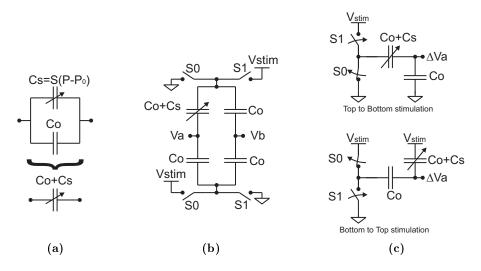

The first step in designing the signal conditioning electronics is to derive a formula which gives the measurement device's signal voltage generation as a function of its pressure sensitivity and the stimulation voltage. Fig. 3.6a gives a simplified model of the capacitive pressure sensor (the parasitic resistances have been omitted), showing that the sensor can be modeled as a nominal capacitance and a pressure sensitive capacitor in parallel resulting in a total sensor capacitance of

$$C_{\text{sensor}} = C_0 + S(P - P_0),$$

where  $C_0$  is the nominal capacitance at the nominal pressure  $P_0$ , S is the sensitivity of the sensor given in Farads/atmosphere, and P is the absolute pressure being applied to the sensor.

Figure 3.6: The circuit diagrams used for calculating the signal voltage as a function of the stimulation voltage and sense capacitance.

- a) The pressure sensitive capacitor equivalent circuit.

- b) The capacitive bridge circuit for generating the signal voltage.

- c) The circuits used for calculating the net change at node  $V_a$  using superposition.

To calculate the signal voltage response to the device's pressure sensitive capacitance, each branch of the capacitive bridge is being stimulated by 2 voltages, a positive going  $V_{\text{stim}}$  and a negative going  $V_{\text{stim}}$ . To find the total voltage change at each branch node, superposition can be applied to the bridge circuit, Fig. 3.6b. Using the equivalent circuits in Fig. 3.6c and calculating the positive (3.2) and negative (3.3) going voltages, and then the summing the voltages (3.4) gives the  $V_a$  node transfer function.

$$\uparrow V a_{{}_{\rm S0\to S1}} = V_{\rm stim} \frac{C_0 + C_s}{2C_0 + C_s} \tag{3.2}$$

$$\downarrow Va_{\rm S0\to S1} = V_{\rm stim} \frac{C_0}{2C_0 + C_s} \tag{3.3}$$

$$\Delta V a_{\rm S0\to S1} = V_{\rm stim} \frac{C_0 + C_s - C_0}{2C_0 + C_s}$$

(3.4)

$$\Delta V a_{\rm S0\to S1} = V_{\rm stim} \frac{C_s}{2C_0 + C_s} \tag{3.5}$$

The transfer function for  $V_b$  is can be derived in exactly the same way, but because  $C_0 - C_0 = 0$ , then

$$\Delta V b_{\rm S0\to S1} = 0,$$

resulting in a function which describes the input signal voltage as a product of the stimulation voltage and the sense capacitance of the pressure sensitive capacitor (3.6), and a capacitance to signal voltage transfer function  $H_{(C_s)}$  of (3.7).

$$V_{\text{signal}} = \Delta V a_{\text{S0} \rightarrow \text{S1}} - \Delta V b_{\text{S0} \rightarrow \text{S1}}$$

$$V_{\text{signal}} = \Delta V a - \Delta V b$$

$$V_{\text{signal}} = V_{\text{stim}} \left(\frac{C_s}{2C_0 + C_s}\right)$$

(3.6)

$$H(C_s) = \frac{C_s}{2C_0 + C_s}$$

(3.7)

In order for the CDC to be able to make full use of the ADC's dynamic range (DR), the signal which is generated by stimulating the capacitive bridge needs to be given an appropriate amount of closed loop gain,  $A_{cl}$ , so that when a full scale pressure is applied to the sensor, there will be a corresponding full scale output voltage.

It should be pointed out that the system is a fully differential system, meaning that the full scale fully differential output voltage is

$$V_{\text{out}_{\text{FS}}} = \pm V_{\text{dd}} = 2V_{\text{dd}}.$$

If the pressure sensing capacitive bridge is stimulated with the stimulation voltage  $V_{\text{stim}}$ , then, across the full scale peak-peak range of the pressure sensing capacitance  $C_{s_{\text{pp}}}$ , the full scale input voltage is

$$V_{\rm in_{FS}} = V_{\rm stim} H(C_{s_{\rm pp}}) = V_{\rm stim} \left( H(C_{s_{\rm max}}) - H(C_{s_{\rm min}}) \right), \tag{3.8}$$

For this design, the stimulation voltage for the capacitive bridge is the supply voltage,  $V_{\text{stim}} = V_{\text{dd}}$ , and the system closed loop gain is therefore (3.10).

$$A_{\rm cl} = \frac{V_{\rm out_{FS}}}{V_{\rm in_{FS}}}$$

$$2V_{\rm dd} = A_{\rm cl} V_{\rm dd} H(C_{s_{\rm pp}})$$

(3.9)

$$A_{\rm cl} = \frac{2}{H(C_{s_{\rm pp}})} \tag{3.10}$$

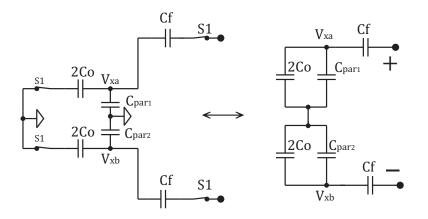

Figure 3.7: The CDS half circuit for finding the closed loop gain.

The closed loop gain of an inverting amplifier is the feedback impedance divided by the input impedance  $Z_f/Z_{in}$ . The top half circuit of the amplifier from Fig. 3.1 is shown again in Fig. 3.7, with the capacitor bridge transformed to show how the input impedance of the CDS system is simply the two branch capacitors in parallel. The feedback impedance from  $C_f$  is  $1/sC_f$ , and the input impedance is  $1/s(2C_0)$ , resulting in (3.11).

$$A_{\rm cl} = \frac{2C_0}{C_f} \tag{3.11}$$

Combining (3.10) and (3.11) will solve for the value of  $C_f$  as a function of the sensor's nominal capacitance and maximum capacitance  $H_{(C_{spp})}(3.12)$ .

$$C_f = C_0 H_{(C_{s_{\rm pp}})} \tag{3.12}$$

In the case where  $C_0 \gg C_s$ , which is the case for the E1.3N capacitive pressure sensor, then (3.7) can reduce to

$$H_{(C_s)} \approx \frac{C_s}{2C_0},\tag{3.13}$$

and the feedback capacitance  $C_f$  would be

$$H_{(C_s = C_{s_{pp}})} \approx \frac{C_{s_{pp}}}{2C_0}$$

$$C_f \approx \frac{C_{s_{pp}}}{2}$$

(3.14)

### 3.1.4 The Final CDS Network Design

At this stage of the design process, because the system supply voltage of  $V_{\rm dd}$  was chosen for the stimulation voltage, the value for  $C_f$  can be calculated based entirely on the desired pressure read range and physical constants intrinsic to the capacitive pressure sensor. The E1.3N pressure sensor has sensitivity  $S \approx 1.6 {\rm pF}/{\rm atmosphere}$ , and a nominal capacitance of  $C_0 \approx 6.0 {\rm pF}$ . For this project, the desired dynamic pressure read range is 1 atm, so  $C_{s_{\rm pp}} = 1.6 {\rm pF}$ , and  $C_f$  is 804 fF from (3.12) (and  $C_f = 800 fF$ when using (3.14)).

At this point, the structure for the pressure sensor's gain stage has been finalized (Fig. 3.1), and the required closed loop gain, and therefore also the value for  $C_f$ , has been calculated based on the desired pressure read range and the amplifier output voltage swing. The next two design requirements concern designing an OTA that can meet the desired sample rate and pressure resolution.

# The Capacitance to Digital Converter Noise Analysis

The capacitance to digital conversion process isn't simply the act of taking the pressure to voltage conversion, amplifying it, and then resolving it to an arbitrary ADC resolution. There will always be some system noise from the amplification stage which will be summed with the pressure sensor sample, and the amount of system noise will determine the maximum usable ADC resolution. Higher resolution ADCs require lower amounts of system noise, and in general, keeping the system noise low requires more power. The ADC and the ADC driver are designed to work with each other. There is no real benefit for over designing the amplification stage if the ADC resolution is low. For example, if the ADC is a 1 bit ADC, then as long as the noise from the amplifier is less than Vdd/2, then the ADC will have no difficulty deciding if the sensor reading is a 1 or a 0. On the other hand, if the power consumption of the circuit must be kept to a minimum, then there is no need to design a 12 bit ADC when the amplifier has a very small signal to noise ratio. To be able to match the OTA performance to a desired pressure resolution it is necessary to define exactly how much noise the CDC system will inject into the noise sample.

Section 4.1 will describe some of the fundamental behaviors of the MOSFET device such as the derivation of the circuit voltage gain and the bandwidth as a function of the device transconductance and load impedance. Section 4.2 will perform a rigorous noise analysis of the switched capacitor capacitance to analog voltage conditioning circuit. The noise analysis will result in a single design equation which describes the total system noise as an inverse function of the OTA noise factor, nf, and the ADC sample and hold input capacitance. This section will also derive the required OTA bandwidth and open loop gain,  $A_0$ , based on the sample rate and ADC resolution accuracy requirements. Section 4.3.1 will cover the derivation of a single general design equation which will return the OTA's maximum allowed noise amplification factor (nf). The nf will be given as a function of the transconductance efficiency ratios,  $\eta_{\rm gm}$ , of each of the OTA's MOSFET devices, and their associated thermal noise coefficient,  $\gamma$ , when operating at that particular level of gm efficiency. And finally, Section 4.4 will discuss the method used to size all of the various transistors to meet the noise factor and the settle time requirements.

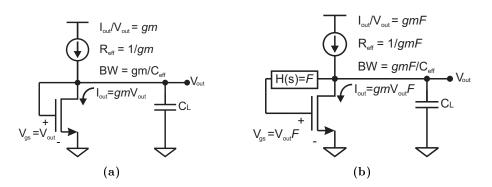

## 4.1 General Transconductance Device Behavior

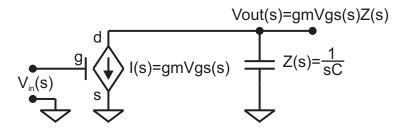

Figure 4.1: The MOSFET small signal model.

The small signal model of a MOSFET driving a capacitance is given in Fig. 4.1. It has an output impedance Z = 1/sC, and an output current to input voltage ratio of gm. Because the current and voltage are inversely related to each other by the factor gm, gm is sometimes modeled as an inverse resistance,  $gm = 1/R_{eff}$ . The output voltage is the output current times the output load which gives the input to output voltage transfer function (4.1).

$$V_{\text{out}}(s) = I(s)Z(s)$$

$$V_{\text{out}}(s) = gmV_{\text{in}}(s)Z(s)$$

$$H(s) = \frac{V_{\text{out}}(s)}{V_{\text{in}}(s)} = gmZ(s)$$

(4.1)

Substituting Z(s) = 1/sC into (4.1), results in the frequency dependent transfer function (4.2), and the frequency where the voltage gain drops to 1 V/V, also known

as the gain bandwidth product (GBW), occurs at  $\omega = gm/C$ , (4.3).

$$H(s) = \frac{gm}{sC} \tag{4.2}$$

$$\omega_{\rm GBW} = \frac{gm}{C} \tag{4.3}$$

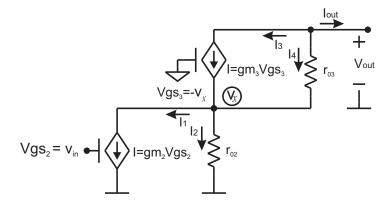

A perfect current source driving a perfect capacitor as in in Fig. 4.1 would have infinite DC voltage gain, but in real life there are no perfect MOSFETs or capacitors. In reality there will be leakage current through the MOSFET (and also a little through the capacitor) as voltage is applied to the drain of the MOSFET, and the current through the MOSFET will will no longer be exactly  $Id = gmV_{gs}$ . The ratio of the change in drain current to change in drain voltage is called the device output conductance gd, and its reciprocal is the output resistance  $1/gd = r_0$ . Fig. 4.2 shows the complete small signal model for the MOSFET driving a load capacitance C.

**Figure 4.2:** An equivalent circuit of a transconductance device with the included device transresistance and reference bias generator.

The output impedance of the circuit from Fig. 4.2 is (4.4), and the small signal transfer function is (4.5). The DC gain of the amplifier is (4.6), and the 3 dB cutoff bandwidth occurs when the denominator magnitude is  $1/\sqrt{2}$  (4.7).

$$Z(s) = \frac{r_0}{sr_0C + 1} \tag{4.4}$$

$$H(s) = gm\left(\frac{r_0}{sr_0C+1}\right) \tag{4.5}$$

$$A_0 = gmr_0 \tag{4.6}$$

$$\omega_{3_{dB}} = \frac{1}{r_0 C} \tag{4.7}$$

The amount of thermal energy delivered from a purely resistive device (such as a resistor) is given as kT,

$$E = kT$$

where k=1.38e-13 is Boltzmann's constant, and T is the temperature in Kelvin. Energy is power times time, and the energy dissipated in a resistor is

$$E = I_{\rm rms}^2 R = \frac{1}{2} I^2 R \ sec$$

where  $I_{\rm rms} = I/sqrt2$ .

From the maximum power transfer theorem, the maximum energy that the resistor can supply to a load is 1/2 of the total energy available from the resistor

$$E_{Resistor} = \frac{1}{4}I^2R \ sec.$$

Equating the kT thermal energy to the amount of energy delivered from the resistor results in a function for the thermal noise current of a resistor.

$$kT = \frac{1}{4}I^2R \ sec$$

$$I^2 = 4kT\frac{1}{R}\Delta f$$

Transconductance is  $gm = 1/R_{eff}$ , but the thermal noise current of the MOSFET does not exactly match the thermal noise current of an equivalent resistor.

$$I_{noise_textMOSFET}^2 \neq 4kT/R_{eff}$$

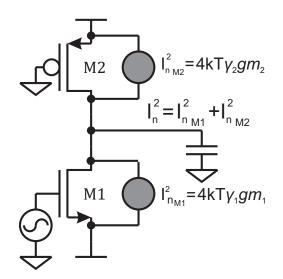

To account for this, it is common to include a noise scaling coefficient,  $\gamma$  [7], for equating the MOSFET noise current to the kT thermal energy. With this  $\gamma$ scaling factor, the MOSFET output noise current is (4.8), and the output current can be input referred to a noise voltage by diving by  $1/gm^2$  (4.9).

$$I_{noise_{\text{out}}}^2 = 4kT\gamma gm \tag{4.8}$$

$$V_{noise_{\rm in}}^2 = 4kT \frac{\gamma}{am} \tag{4.9}$$

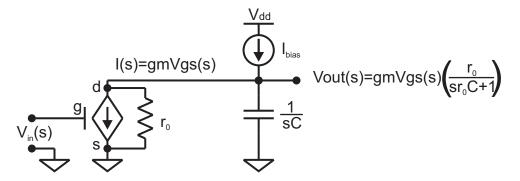

The MOSFET device in Fig. 4.2 is getting its bias current from a perfect current source which does not have any associated noise current, but in reality, there is no such thing as a perfect current source. Instead, the current source itself will be a MOSFET biased at a DC voltage with its own  $4kT\gamma gm$  noise current contribution.

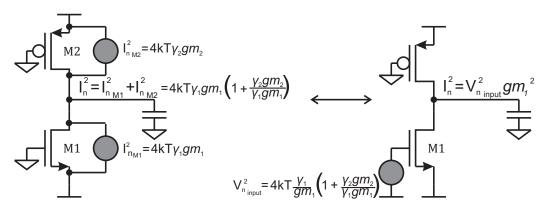

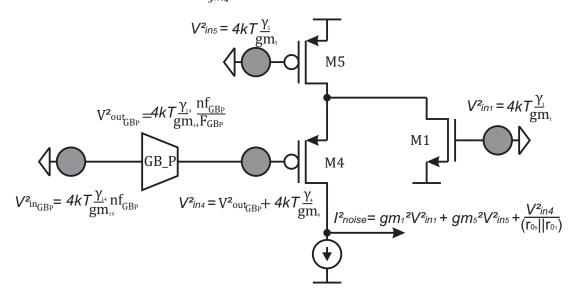

Figure 4.3: Input referred system noise current

How much extra noise current is being supplied by the load is very dependent on the load circuit. Later in this chapter, Sec. 4.3.1, a full derivation of the total amount of extra noise current is given. However, for the time being, the total input referred noise of the amplifier is given as the input device input referred thermal noise voltage, (4.9), multiplied by a thermal noise factor nf (4.10).

$$V_{noise_{\rm in}}^2 = 4kT \frac{\gamma}{gm} nf, \qquad (4.10)$$

where nf is simply a scaling factor which is used to input refer the total output noise current to the input device's gm.

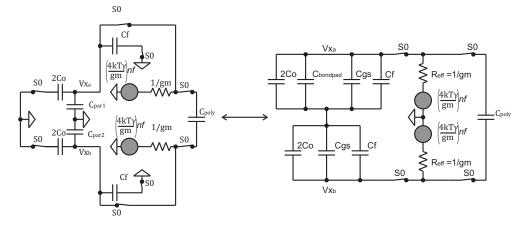

## 4.2 SC Noise Analysis

The SC amplifier is a fully differential SC amplifier with input and output offset cancellation circuitry (Fig. 4.4) [6]. In Fig. 4.5a, during SC switch phase S0, the amplifier is in reset configuration where the OTA's DC offset voltage  $V_{os}$  and the system noise voltage  $V_{x_{ab}S0noise}$  are sampled across the nodes  $V_{x_{ab}}$  (4.11). During phase S1, Fig. 4.5b,  $V_{os}$ , the system noise voltage  $V_{x_{ab}S1noise}$ , and the capacitance to voltage conversion result are sampled across  $V_{x_{ab}}$  (4.12).

$$V_{x_{ab}S0} = V_{os} + V_{x_{ab}S0noise} \tag{4.11}$$

$$V_{x_{ab}S1} = V_{os} + V_{x_{ab}S1noise} + \Delta V_{ab} \tag{4.12}$$

$$V_{x_{ab}S1} - V_{x_{ab}S0} = \Delta V_{ab} + V_{x_{ab}S0noise} + V_{x_{ab}S1noise}$$

(4.13)

Taking the difference between (4.12) and (4.11) results in (4.13). The noises are variance, and they are therefore summed together, but the offset voltage is deterministic, and is therefore subtracted away leaving only the conversion signal and the noise from the two sample stages.

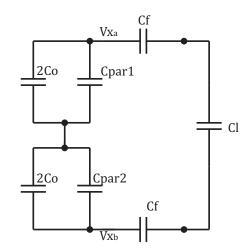

Figure 4.4: Schematic of the capacitive bridge and the SC amplifier with associated parasitic capacitances

## 4.2.1 SC Noise Analysis for Phase S0

To determine the noise from switching phase S0, the SC amplifier circuit from Fig. 4.4 can be reduced to the circuit in Figure 4.6. To find the amount of rms noise voltage sampled across  $V_{x_{ab}}$  while the OTA is in reset, the noise voltage across  $V_{x_{ab}}$  needs to be integrated over all frequencies. Looking at Fig. 4.6, the signal across  $V_{x_{ab}}$  is simply the OTA output voltage, which in the reset phase is just the sum of the two input referred noise voltages (4.10), multiplied by the frequency dependent circuit transfer function

Figure 4.5: Simplified circuit diagram of the SC amplifier in its two switch phases.

**Figure 4.6:** Schematic of the SC amplifier during phase S0 with the equivalent circuit for deriving  $C_{eq}$ .

across the equivalent capacitance,  $C_{eq}$ . The differential load capacitance across the outputs of the OTA during switching phase S0 in Fig. 4.6 can be derived as follows  $C_{eq}$  (4.14).

$$C_{eq_a} = 2C_0 + C_{par1} + C_f$$

$$C_{eq_b} = 2C_0 + C_{par2} + C_f$$

$$C_{eq} = \frac{C_{eq_a}C_{eq_b}}{C_{eq_a} + C_{eq_b}} + C_{poly}$$

(4.14)

Using  $C_{eq}$ , the  $\omega_{3_{dB}}$  cutoff frequency in radians is

$$\omega_{3_{\rm dB}} = \frac{1}{C_{eq}(2R_{eff})}$$

the transfer function from the noise voltage generator to the  $V_{\!x_{ab}}$  nodes is

$$H(j\omega) = \frac{1}{j\frac{\omega}{\omega_{3_{dB}}} + 1}$$

$$H(j\omega) = \frac{1}{j\omega C_{eq}(2R_{eff}) + 1}$$

$$H(j\omega) = \frac{1}{j\omega\frac{2C_{eq}}{gm_1} + 1},$$

(4.15)

and the frequency dependent output noise voltage at  $V_{x_{ab}}$  is (4.16).

$$V_{out_{\text{noise}}}^2 = 8kT \frac{\gamma_1}{gm_1} nf \left(\frac{1}{j\omega \frac{2C_{eq}}{gm_1} + 1}\right)^2$$

(4.16)

The last step for finding the total rms noise is to integrate (4.16) for all frequencies from DC to infinity. Once this integration is complete, the total rms noise for the CDC system while it is being held in switch phase S0 is (4.18).

$$V_{noise_{\rm rms}}^{2} = 8kT \frac{\gamma_{1}}{gm_{1}} nf \int_{0}^{\infty} \left| \frac{1}{j\omega \frac{2C_{eq}}{gm_{1}} + 1} \right|^{2} d\omega$$

$$V_{noise_{\rm rms}}^{2} = 8kT \frac{\gamma_{1}}{gm_{1}} nf \left( \frac{1}{4\frac{2C_{eq}}{gm_{1}}} \right)$$

(4.17)

$$V_{x_{ab}S0noise}^2 = \frac{kT}{C_{eq}}\gamma_1 nf \tag{4.18}$$

It should be pointed out here that for a first order transfer function decaying at 20 dB/decade from  $\omega_{3_{\text{dB}}}$ , such as (4.15), its integral from zero to infinity is 1/4 of its cutoff frequency in radians (4.19) [8].

$$\oint_{0}^{\infty} \left| \frac{1}{j \frac{\omega}{\omega_{3_{dB}}} + 1} \right|^{2} d\omega = \frac{\omega_{3_{dB}}}{4}$$

$$NEB^{=} \frac{\omega_{3_{dB}}}{4}$$

(4.19)

This factor is commonly called the noise equivalent bandwidth, (NEB), and it will be used several more times throughout the design process.

As the SC amplifier switches to phase S1, the OTA drives the nodes  $V_{x_a}$  and  $V_{x_b}$  to virtual ground, and the noise charge which was sampled onto  $V_{x_{ab}}$  during SC phase

Figure 4.7: Equivalent schematic for deriving the phase S1 feedback factor (4.22)

S0 (4.18) gets transferred to the output nodes as a function of the feedback gain. To determine the switch phase S1 voltage gain from  $V_{x_{ab}}$  to the output nodes it is only necessary to know the transfer function from output to input. Fig. 4.7 can be used to help determined the feedback factor from output to input. This term is commonly referred to as the feedback factor F, where  $F = V_{x_{ab}}/V_{out}$ . Taking  $V_{x_{ab}}$  and multiplying by 1/F gives the output voltage.

$$V_{out} = \frac{V_{x_{ab}}}{F},\tag{4.20}$$

and by combining (4.18) and (4.20), the final end of conversion output noise contribution from phase S0 is (4.21).

$$V_{out_{noise}_{S0}}^{2} = \frac{V_{x_{ab}S0noise}^{2}}{F^{2}}$$

$$V_{out_{noise}_{S0}}^{2} = \frac{kT}{C_{eq}} \frac{\gamma_{in} nf}{F^{2}}$$

(4.21)

With the help of the equivalent circuit from Fig. 4.7, the calculation of F as the capacitive voltage divider from  $V_{out}$  to  $V_{x_{ab}}$  is fairly straight forward with the result being (4.22).

$$F = \frac{V_{x_{ab}}}{V_{out}} = \frac{C_f}{C_f + 2\left(\frac{(2C_0 + C_{par1})(2C_0 + C_{par2})}{(2C_0 + C_{par1}) + (2C_0 + C_{par2})}\right)}$$

(4.22)

According to (4.18), the greater the value for  $C_{eq}$ , the smaller the S0  $V_{x_{ab}}$  noise voltage.  $C_0$  and  $C_f$  are fixed values determined by the sensor's nominal capacitance and the required closed loop gain, but  $C_{eq}$  can be made larger by increasing the other capacitances. However, increasing  $C_{par}$  will, according to (4.22), reduce the feedback factor which will result in greater phase S0 output noise (4.21).

The solution for reducing the phase S0 noise level while not reducing the amount of phase S1 feedback factor is to use the capacitor  $C_{\text{poly}}$ .  $C_{\text{poly}}$  is part of  $C_{eq}$  (4.14), but it is not part of F (4.22). Meaning it helps to reduce the phase S0 noise voltage, but the noise charge stored on its plates is not transferred to the output as noise voltage during phase S1. Also, because the OTA is in reset,  $C_{\text{poly}}$  can be  $A_{cl}$  times greater than the ADC sample and hold capacitor without having a negative impact on the reset phase S0 settling bandwidth.

#### 4.2.2 SC Noise Analysis for Phase S1